本帖最后由 feifeiz 于 2023-5-13 23:33 编辑

一、前言

在上一篇文章中学习了IP之FIFO,对IP以及FIFO进行了解,通过开发板测试以及仿真分析验证了设计思想,说到IP,一直打算在PGL22G开发板上实现一个软核,但是没找到相关资料以及相关说明,唯一找到过一个集创赛有一个Cortex-M1 SoC,可惜没有放出来,如果有资料,很愿意尝试软核的搭建使用。软核当前是搭建不了了,因此本次选用了一个其他功能进行试验,本次实现HDMI彩条输出试验。

二、HDMI简介

HDMI,全称为(High Definition Multimedia Interface)高清多媒体接口,主要用于传输高清音视频信号,是新一代的多媒体接口标准。它能够同时传输视频和音频,简化了设备的接口和连线;同时提供了更高的数据传输带宽,可以传输无压缩的数字音频及高分辨率视频信号。

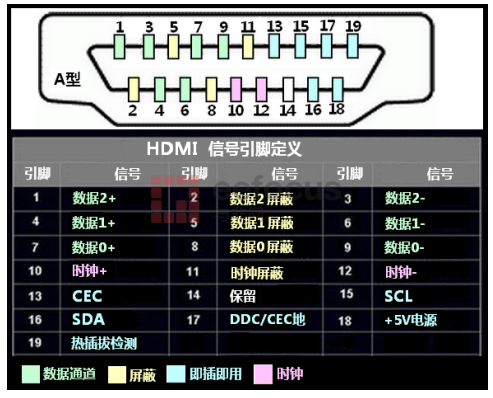

引脚接口定义:

其中主要的硬件为TMDS,SCL,SDA,HOT PLUG,+5V,TMDS引脚包括TMDS CLOCK、TMDS DATA[2:0],用于传输RGB数字信号、音频信号等,SCL、SDA引脚主要用于获取显示器的EDID信息。HOT PLUG该引脚主要用于显示器通知主机是否插好。

三、实验目标

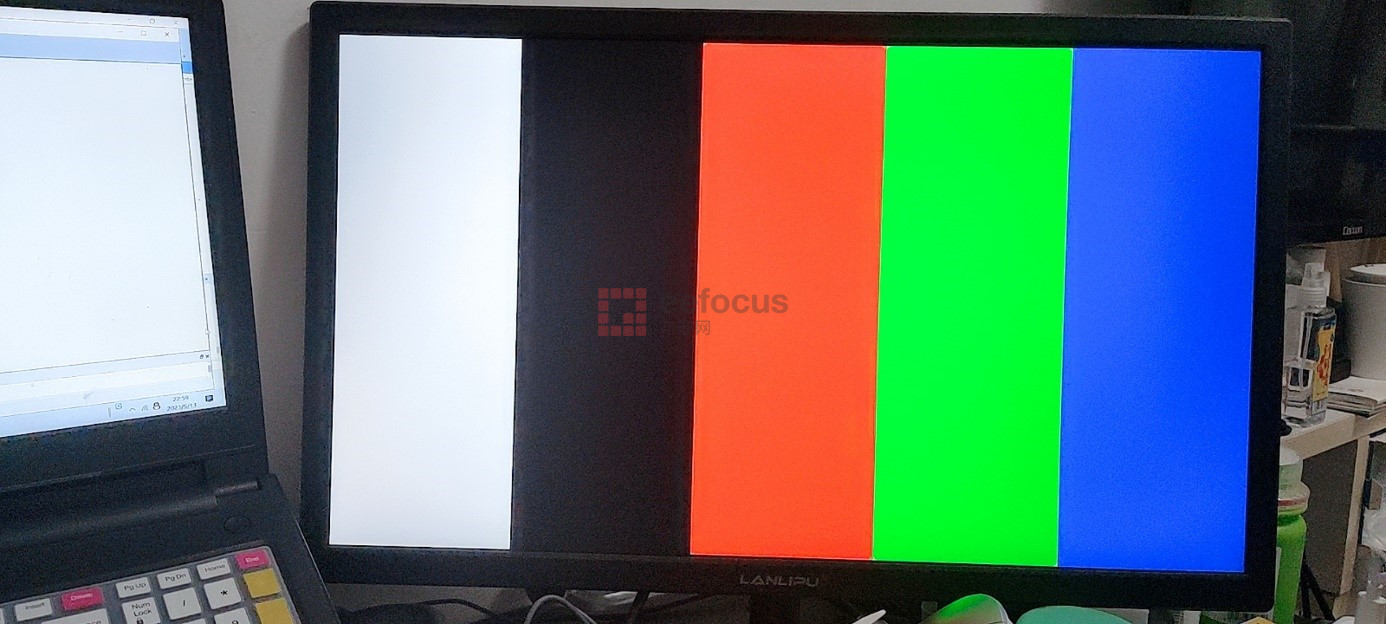

使用板载的HDMI接口驱动电脑显示屏上显示彩条,由于板板子只支持720P,电脑屏幕为1080P的,在实际显示的时候不能显示在整个屏幕上。

四、硬件设计

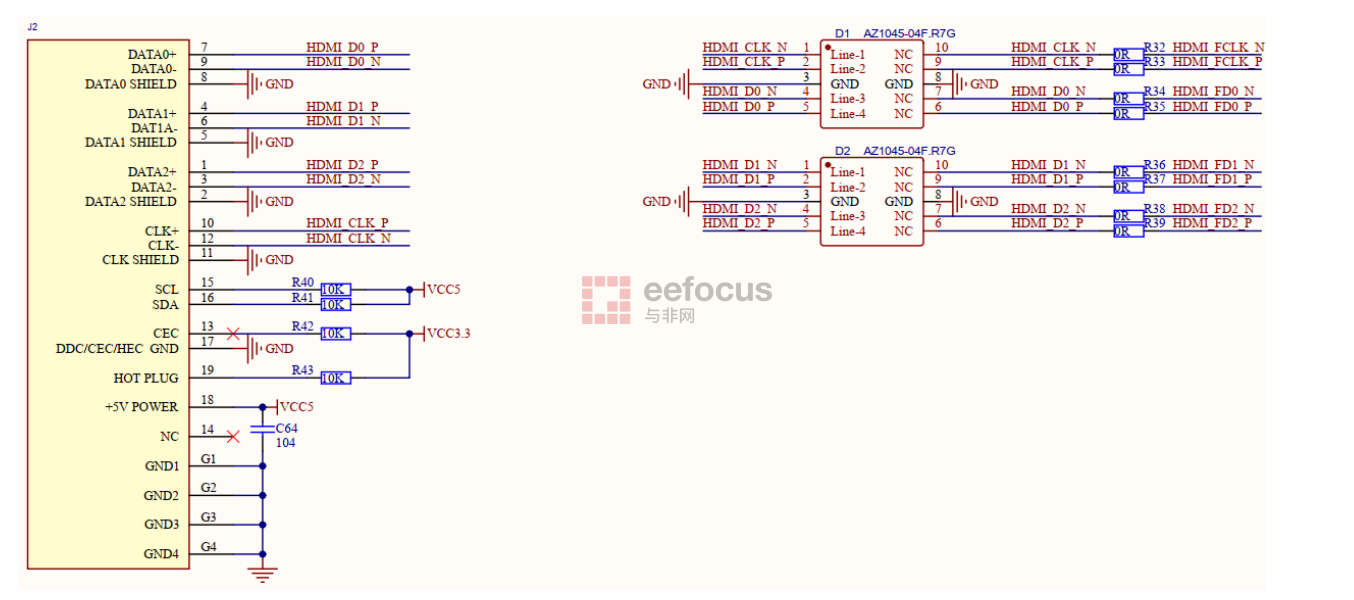

HDMI 的三个数据通道HDMI_D[2:0]和一个时钟通道 HDMI_CLK 直接与 FPGA 的 TMDS 差分引脚相连,硬件原理图如下:

管脚分配如下:

信号名称

| 方向

| 管脚

| 说明

| Sys_clk

| input

| B5

| 系统时钟,50M

| Sys_rst_n

| input

| G5

| 系统复位

| tmds_data_p[2]

| output

| R16

| TMDS 数据通道2(正极)

| tmds_data_p[1]

| output

| U14

| TMDS 数据通道1(正极)

| tmds_data_p[0]

| output

| U15

| TMDS 数据通道0(正极)

| tmds_clk_p

| output

| P17

| TMDS 时钟通道(正极)

| tmds_data_n[2]

| output

| T16

| TMDS 数据通道2(负极)

| tmds_data_n[1]

| output

| V14

| TMDS 数据通道1(负极)

| tmds_data_n[0]

| output

| V15

| TMDS 数据通道0(负极)

| tmds_clk_n

| output

| P18

| TMDS 时钟通道(负极)

|

五、程序设计

总体设计,HDMI彩条实验只需要显示图像,不需要识别显示器是否插入,不需要识别显示器的EDID数据,此时可以将HDMI当作DVI接口去驱动。总体框图如下:

在顶层模块中,video_display模块负责产生RGB888格式的彩条图案,然后在video_driver模块的驱动下按照工业标准的VGA显示时序输出视频信号、行场同步信号以及视频有效信号。这些信号作为RGB2DVI模块的输入,最终转换成DVI/HDMI接口标准的TMDS串行数据输出到HDMI接口。

顶层模块设计:

modulehdmi_colorbar_top(

input sys_clk,

input sys_rst_n,

output tmds_clk_p, // TMDS 时钟通道

output tmds_clk_n,

output [2:0] tmds_data_p, // TMDS数据通道 output [2:0] tmds_data_n

);

//wire define

wire pixel_clk;

wire pixel_clk_5x;

wire clk_locked;

wire [10:0] pixel_xpos_w;

wire [10:0] pixel_ypos_w;

wire [23:0] pixel_data_w;

wire video_hs;

wire video_vs;

wire video_de;

wire [23:0] video_rgb;

//*****************************************************

//** main code

//*****************************************************

//例化PLL IP核

pll_clk u_pll_clk(

.pll_rst (~sys_rst_n),

.clkin1 (sys_clk),

.clkout0 (pixel_clk), //像素时钟

.clkout1 (pixel_clk_5x), //5倍像素时钟

.pll_lock (clk_locked)

);

//例化视频显示驱动模块

video_driver u_video_driver(

.pixel_clk (pixel_clk),

.sys_rst_n (sys_rst_n),

.video_hs (video_hs),

.video_vs (video_vs),

.video_de (video_de),

.video_rgb (video_rgb),

.pixel_xpos (pixel_xpos_w),

.pixel_ypos (pixel_ypos_w),

.pixel_data (pixel_data_w)

);

//例化视频显示模块

video_display u_video_display(

.pixel_clk (pixel_clk),

.sys_rst_n (sys_rst_n),

.pixel_xpos (pixel_xpos_w),

.pixel_ypos (pixel_ypos_w),

.pixel_data (pixel_data_w)

);

//例化HDMI驱动模块

dvi_transmitter_top u_rgb2dvi_0(

.pclk (pixel_clk),

.pclk_x5 (pixel_clk_5x),

.reset_n (sys_rst_n &clk_locked), .video_din (video_rgb),

.video_hsync (video_hs),

.video_vsync (video_vs),

.video_de (video_de),

.tmds_clk_p (tmds_clk_p),

.tmds_clk_n (tmds_clk_n),

.tmds_data_p (tmds_data_p),

.tmds_data_n (tmds_data_n)

);

endmodule

显示模块:

模块实现1280x720的分辨率。模块输入变量为像素点横纵坐标,来自于video_driver模块;根据像素坐标,输出该像素坐标的数据。

module video_display(

input pixel_clk,

input sys_rst_n,

input [10:0] pixel_xpos, //像素点横坐标 input [10:0] pixel_ypos, //像素点纵坐标 output reg [23:0] pixel_data //像素点数据 );

//parameter define

parameter H_DISP =11'd1280; //分辨率——行 parameter V_DISP =11'd720; //分辨率——列

localparam WHITE =24'b11111111_11111111_11111111; //RGB888白色 localparam BLACK =24'b00000000_00000000_00000000; //RGB888黑色 localparam RED =24'b11111111_00001100_00000000; //RGB888红色 localparam GREEN =24'b00000000_11111111_00000000; //RGB888绿色 localparam BLUE =24'b00000000_00000000_11111111; //RGB888蓝色

//*****************************************************

//** main code

//*****************************************************

//根据当前像素点坐标指定当前像素点颜色数据,在屏幕上显示彩条

always @(posedge pixel_clk ) begin

if (!sys_rst_n)

pixel_data <=16'd0; else begin

if((pixel_xpos >=0) && (pixel_xpos < (H_DISP/5)*1)) pixel_data <=WHITE; else if((pixel_xpos>= (H_DISP/5)*1) && (pixel_xpos < (H_DISP/5)*2)) pixel_data <=BLACK; else if((pixel_xpos>= (H_DISP/5)*2) && (pixel_xpos < (H_DISP/5)*3)) pixel_data <=RED; else if((pixel_xpos>= (H_DISP/5)*3) && (pixel_xpos < (H_DISP/5)*4)) pixel_data <=GREEN; else

pixel_data <=BLUE; end

end

endmodule

六、实验现象

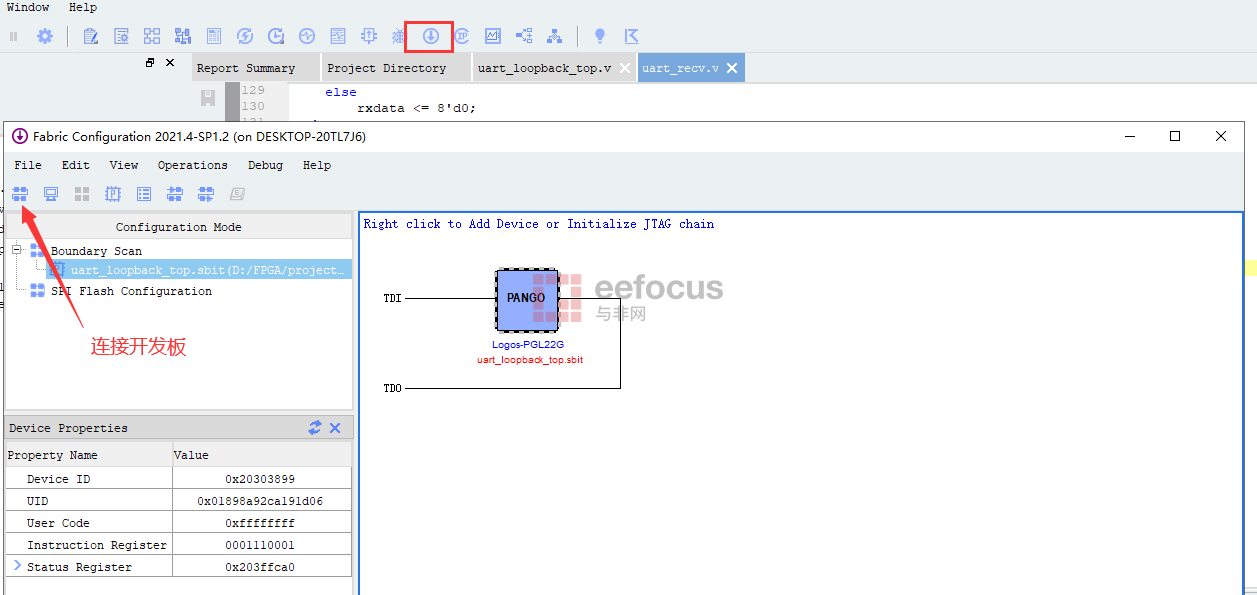

编译工程,生成.sbit文件

连接开发板

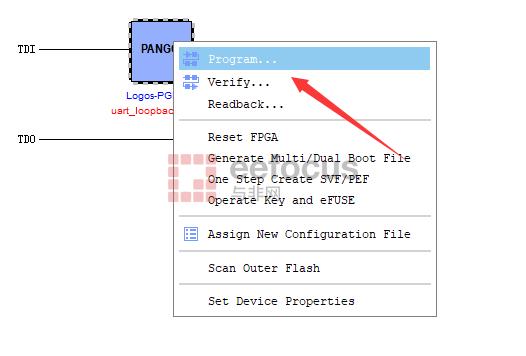

下载

运行结果:

|  /1

/1

/1

/1