TA的每日心情 | 奋斗

2014-6-4 13:58 |

|---|

签到天数: 188 天 连续签到: 1 天 [LV.7]常住居民III

|

本帖最后由 zwj108 于 2013-8-8 20:33 编辑

1 引 言

步进电机是一种将数字信号转换为角位移或线性位移的控制驱动装置。它的速度和控制脉冲严格同步,响应速度极快,有较高的重复定位精度,大量应用在精密控制的场合。常用的步进电机控制系统,采用微机控制,用软件实现其步进脉冲的产生。这种方法程序量大,占用CPU时间较多,限制了步进电机速度的进一步提高,而且软件方式的抗干扰性能较差,在EMI较严重的场合其可靠性不如纯硬件电路。在硬件中,环形分配器逻辑关系复杂,用传统的分立元件实现,电路规模大,连接线复杂,灵活性差,功耗较大,其系统可靠性也不尽人意。

在传统的系统设计流程中,通常采用MCS-51单片机作为整个系统的主控制器,MCS-51单片机实现整个系统外设的管理和控制功能。但是从工程设计角度看,51单片机的I/O端口数量较少资源有限,而且单片机程序执行具有顺序性,因此51单片机只能通过外接端口扩展芯片,并采用分时操作的方式来实现对整个外设的控制和管理。相对于51单片机而言,FPGA器件具有硬件速度快、I/O端口数目更多、并行处理能力更强的优点,能够利用丰富的可编程资源针对不同的外设构造相应的逻辑电路,从而实现对外设接口的管理及控制。

2 芯片设计思想概述

2. 1 总体架构

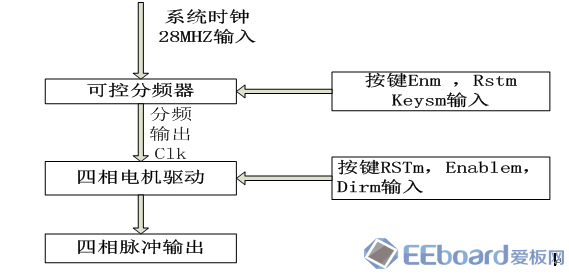

整个芯片采用模块化设计方式,实现“手动”控制电机的“运转/停止”;当电机处于“运转”状态时,可“动态调节”电机的转速和方向;当步进电机每次接受到一组脉冲信号,便旋转一个角度。

2. 2 各部分功能分析

时钟分频控制部分:该部分实际上是用按键Keys和EN输入控制FPGA输出频率从而实现电机转速快慢的。

驱动逻辑控制部分:该部分包括模式选择,复位控制,方向控制。

3 各模块的设计

根据各部分的功能,将全系统分为时钟分频控制模块、驱动逻辑控制模块和顶层模块三部分。

各模块关系如图1所示。

3. 1 时钟分频控制电路的设计

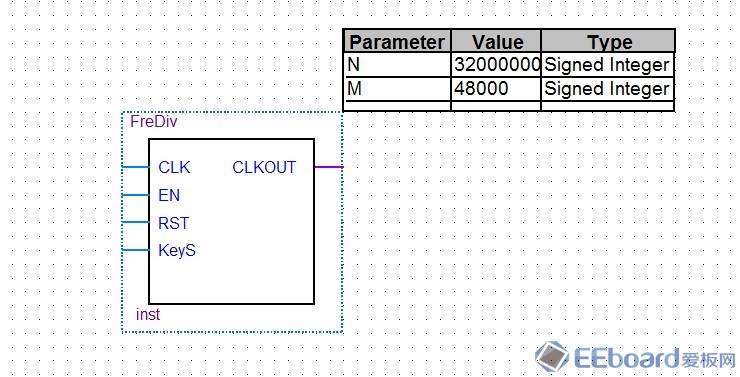

通过按键Keys和EN输入控制FPGA输出频率多少从而实现电机转速快慢的目的。根据步进电机时钟频率的要求,尤其是空载时的启动频率很低大约为300HZ左右,而该FPGA系统板的时钟为28MHZ,所以在系统上电时的频率就应该在300HZ左右,修改下面的N,M和temp2参数就可以设定系统上电时的输出频率

在该模块中,包含两个进程,分别将时钟信号上升沿以及按键上升沿设置为触发的敏感事件。当EN=1,按动Keys加快电机转速;当EN=0,按动Keys减缓电机转速。每个Verilog 模块以module开头, 以endmodule 结束。下面给出时钟分频控制模块源程序:

module FreDiv(CLK,CLKOUT,EN,RST,KeyS);

input CLK,RST,KeyS,EN;

output CLKOUT;

parameter N=32000000,M=48000 ; // 计数器二进制位数

integer temp1=0,temp2=96000;

always @(posedge CLK)

begin

if (!RST)

begin

if (temp1>=temp2-1)temp1<=0;

else temp1<=temp1+1;

end

end

always @(posedge KeyS)

begin

if (KeyS & EN)

begin

if(temp2==N-1)temp2<=N/2;

else temp2<=temp2+1000;

end

if (KeyS & ~EN)

begin

if(temp2==0)temp2<=N/2;

else temp2<=temp2-1000;

end

end

assign CLKOUT=(temp1<M)?1:0;

endmodule

endmodule

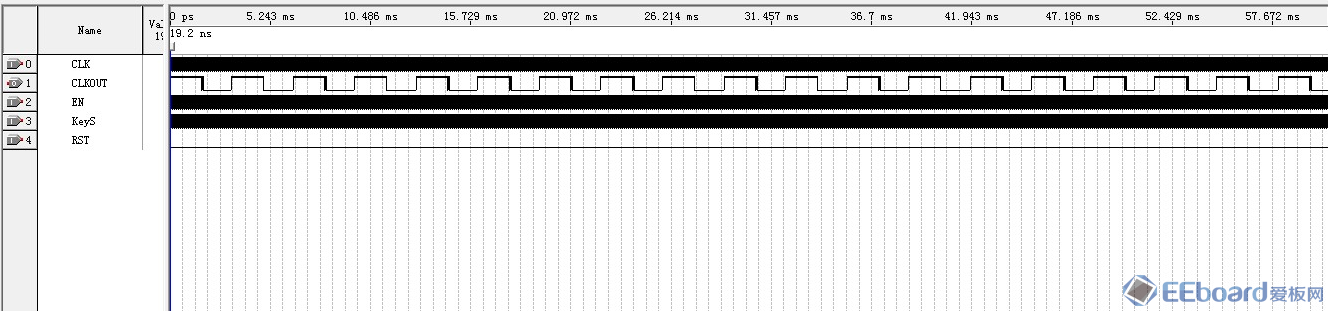

为验证以上程序是否满足设计要求,我们在Active-HDL仿真平台下进行了时序功能验证。其仿真波形如图2所示。

图2 由仿真波形可见,满足设计的功能要求。

生成RTL图如图3所示:

图3 3. 2 驱动逻辑控制模块电路设计

本电路是驱动电机转动和控制电机转向及复位的模块。

电机驱动模块用L298N电路图:

源程序如下:

module Motor(Out, Clk, Dir,Enable, Rst);

input Clk;

input Dir;

input Enable;

input Rst;

output[3:0]Out;

reg[3:0] Out;

reg[2:0] state;

always @(posedge Clk or negedge Rst)

begin

if ( !Rst) //低电平复位,初始化设置

begin

Out<= 4'b0;

state<= 3'b0;

end

else

begin

if(Enable == 1'b1)

if (Dir == 1'b1) state = state + 3'b001 ; //正转

else if (Dir == 1'b0) state = state-3'b001 ; //反转

case (state)

3'b000 : Out = 4'b0001 ;

3'b001 : Out = 4'b0011 ;

3'b010 : Out = 4'b0010 ;

3'b011 : Out = 4'b0110 ;

3'b100 : Out = 4'b0100 ;

3'b101 : Out = 4'b1100 ;

3'b110 : Out = 4'b1000 ;

3'b111 : Out = 4'b1001 ;

endcase

end

end

endmodule

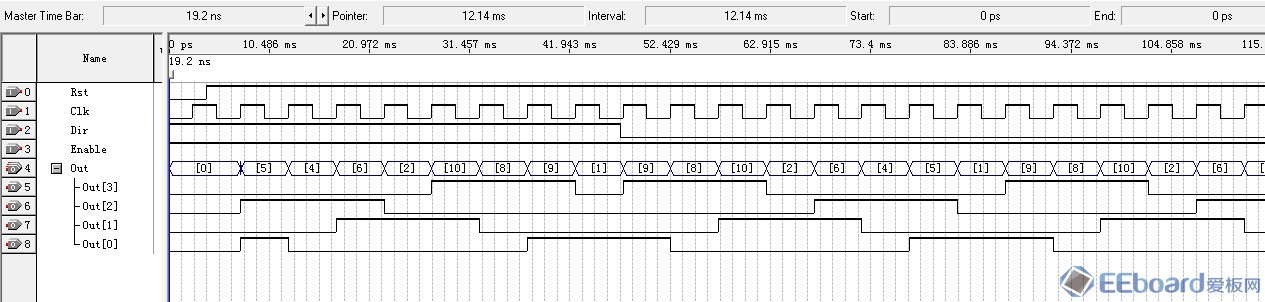

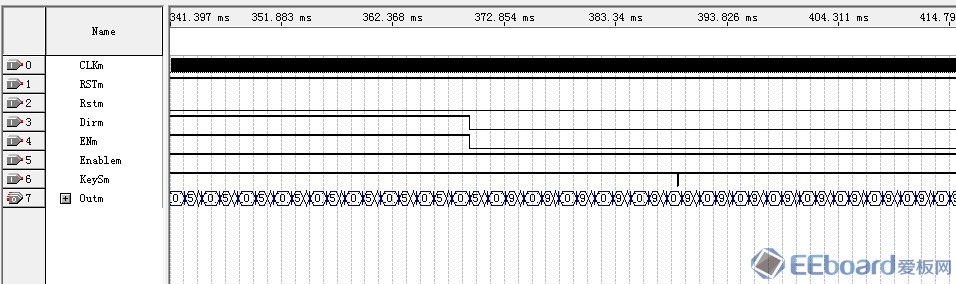

仿真波形如图5所示:

图5 由上图可以看出,实现了四相步调脉冲的输出以及正反转,复位功能。

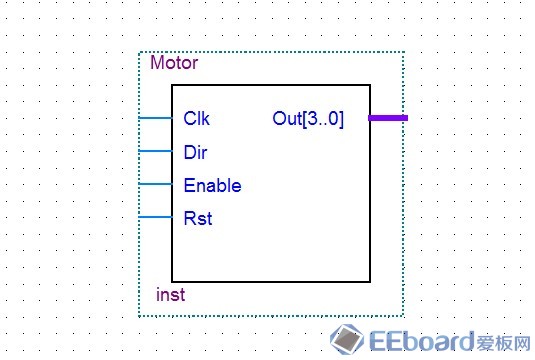

生成RTL图如图6所示:

图6 3. 3 顶层模块设计

顶层模块就是把前面的时钟分频模块和电机驱动模块综合。其中包括有复位控制,方向控制及转速控制。因此,根据系统控制要求,调用上述所有的模块,是顶层模块的主要任务。

顶层设计源程序如下:

module StepMotor(CLKm,ENm,KeySm,Outm,Dirm,Enablem,RSTm,Rstm);

input CLKm,ENm,KeySm,Dirm,Enablem,RSTm,Rstm;

output[3:0] Outm;

wire clk;

Motor u1(Outm,clk,Dirm,Enablem,RSTm);

FreDiv u2(CLKm,clk,ENm,Rstm,KeySm);

endmodule

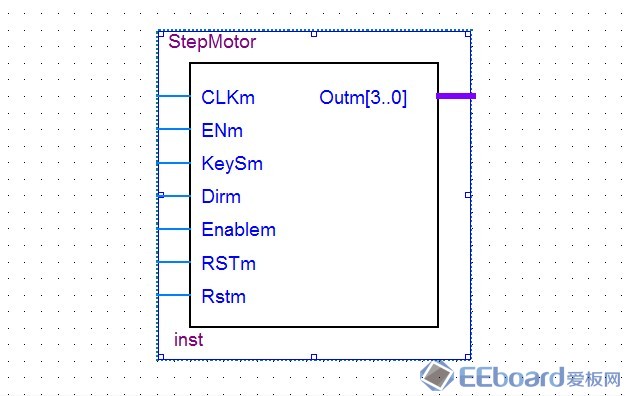

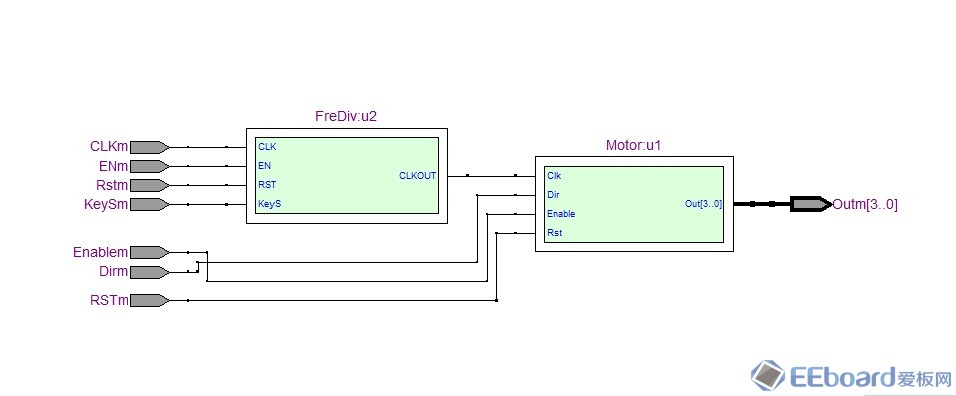

生成RTL图如图7所示:

图7 时序仿真图如下图

由于各模块的独立性,在物理测试过程中可对各模块分开综合调试,以此确保硬件电路能同时满足预期的功能和逻辑约束条件。

4 结束语

本系统在硬件设计上采用了模块化设计,通过数字示波器检测FPGA各输出的频率及输出波形,均达到目的要求。

本方案已完全实现, 系统运行良好。

|

-

|

/2

/2

/2

/2