|

近期根据对 ASIC 设计人员团队的调研,发现在所有的设计项目中,超过 70% 的设计项目在测试芯片流片前采用某种形式的基于 FPGA 的原型来构建设计的高速模型。这种原型有助于在设计周期中尽早启动软件开发工作和完成功能覆盖。在许多公司中,采用商用的基于 FPGA 的原型系统所具备的多用性和重用优势较公司内部开发的定制电路板可带来更高的投资回报。 Synopsys HAPS 高性能 ASIC 原型系统长期以来一直使用赛灵思Virtex® FPGA 作为 ASIC 原型的逻辑主机 (logic host)。HAPS 电路板系统最早由位于瑞典 Lund 的 HARDIElectronics AB (现为 Synopsys 公司硬件平台部的下属单位) 开发,经数以千计的原型项目验证,是一款成功的多功能工具。究其原因,有必要对构成这种先进的解决方案的 Virtex-6 和HAPS 系统架构的功能元件进行更深入的了解。 Virtex-6 是 ASIC 原型的理想选择

在 HAPS 原型系统的整个发展历程中,至始至终采用 Virtex 系列器件,其中包括 Virtex-II、Virtex-II Pro、Virtex-4、Virtex-5 和最新的 Virtex-6LX760 器件。世界最大容量的 LX760已经在许多公司中证明其作为 ASIC 原型设计工具的实用性。设计人员可以同时将该器件的可编程功能和嵌入式模块功能用于原型设计工作。 主要的 LX760 逻辑构建块 (即Slice) 由可编程查找表 (LUT)、用于实现组合功能的存储单元以及小型 RAMBlock 或移位寄存器构成。LX760 中共有 118,560 个可用的 Slice,为原型ASIC RTL 提供充足的资源用于实现主机逻辑功能,比如奇偶校验、XOR、AND、OR 和同步逻辑。对于乘法器、累加器及其它 DSP 逻辑等算术功能的移植,LX760 能提供比基于 slice 的逻辑单元面积使用率高得多的嵌入式信号处理模块。除 DSP48E1 模块外,LX760 还可提供 864 个 DSP 模块,每个 DSP 模块由一个 25x18 位二进制补码乘法器和一个 48 位累加器构成。Synopsys Synplify Premier FPGA 逻辑综合工具能够自动针对这些必要的构建块提供最佳时钟性能。 片上系统 (SoC) 设计涉及多种存储器,或由目标 ASIC 晶圆厂的存储器库提供,或由存储器编译器生成。在大多数情况下,FPGA 能够有效地运用这些存储器,将 Slice 对应较小的寄存器文件,嵌入式 Block RAM 对应较大、较深的阵列,或对应最大型的存储器,将HAPS 的存储器子板用作主机。有效的ASIC 存储器移植是基于 FPGA 的原型方法的组成部分,往往涉及分配一个替代性的 FPGA 友好型实现来保证对片上RAM 最有效的利用。例如,可以使用Verilog HDL 的“Define”来驱动替代设计,以便在代码指向不同的实现时在模块之间轻松完成切换。在许多情况下,可以用 ASIC 存储器编译器生成模型的“仿真友好型”轻量版。这个轻量版不含测试逻辑,故原型设计能够更容易地移植到原型系统。Virtex-6 760LX 可为托管存储模块提供多达 8,280Kb 的基于 Slice 的分布式 RAM 和 25,920Kb的 Block RAM。 Virtex-6 系列提供了多达 9 个基于 PLL 的嵌入式混合模式时钟管理器(MMCM),可用作宽频带上的频率综合器、内部或外部时钟的抖动滤波器,以及去歪斜时钟。Virtex-6 的MCMM 的输出频率可从 4.69MHz 到800MHz。这对需要实现内部时钟数MHz 速率的原型来说是一种重要的资源。Synopsys Certify 多 FPGA 原型环境能够依据按设计分区情况生成的时钟分布 IP 配置 HAPS 系统的板载PLL 和嵌入式 LX760 MMCM,从而简化 ASIC 时钟的实现。 HAPS 应用的模块化架构

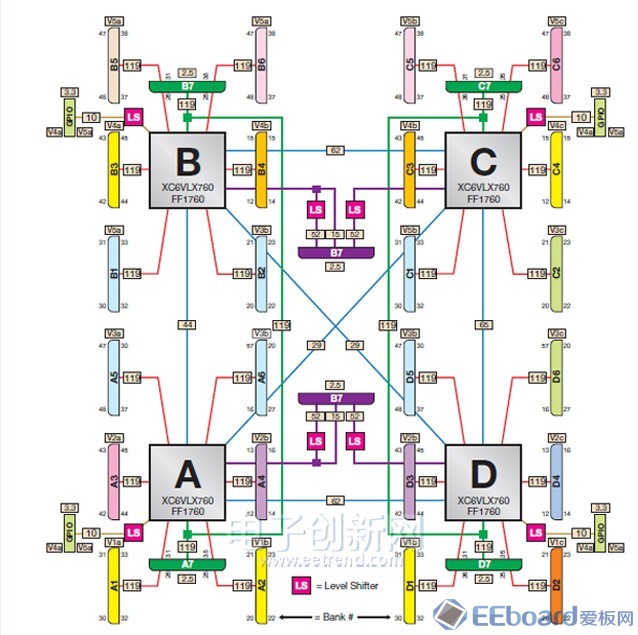

HAPS 设计小组依据一些关键设计标准来平衡原型线路板的成本、性能和连接功能需求。对 ASIC 仿真器等硬件辅助验证工具而言,RTL 调试与验证是主要的应用。但原型社区更关注的是“验证”,这个过程涉及的测试场景五花八门。这就要求原型有足够高的性能,不仅能够与千兆位以太网和双沿数据 (DDR) 存储器接口等真实世界协议相连, 而且还可运行SoC 处理器以启动操作系统。 鉴于这些问题,硬件设计人员决定提供一种非常开放的模块化架构,结合 FPGA 之间的可重配置的互联方案,最大限度地提高 FPGA I/O 的访问能力。为实现 Virtex I/O bank 的 I/O、控制和电源信号访问能力的最大化,我们开发了一种专门用于原型PCB 的专用连接器(见侧边栏),即HapsTrak 标准。子板提供 PCIe®、DDR 存储器和 USB 等常用标准的专用物理接口。HAPS 子板使用相同的HapsTrak 标准公/母连接器。 HAPS-64 系统将四个 XC6VLX760-FF1760 器件结合在一起,构成了一种“超级 FPGA”平台,其容量多达 1,800 万ASIC 门。有如此大的逻辑容量可供使用,HAPS 设计小组可用 HapsTrak 连接器将 I/O 以及FPGA 间总线连接成正则矩阵,用于支持系统的堆叠或连线。每个 FPGA均与一组这样的连接器相连,每个连接器都有专门的引脚用于电源和时钟。板载的埋线提供了更多 FPGA 连接。互联开发板可带来更宽的总线。总线的一部分连接到两对 HapsTrak 连接器上, 用于将总线延伸到其它系统、子板和测试设备。所有 HAPS 系统在底部均采用公母配套连接器,故可以堆叠在一起。这种非常开放的 I/O方案为 ASIC 原型设计人员提供了大量的扩展和连接功能选项。

在任何电路板设计中,都要着重考虑到时钟管理, 原型系统也是如此。以板载 PLL 或外部时钟发生器为时钟源的板载全局时钟分配树可避免歪斜并提供充足的扇出缓存驱动强度,确保高速运行下良好的健全性。该设计为 HAPS 母板上的 FPGA 提供了一个大容量时钟走线池,共有 299个差分时钟信号输入到 FPGA 中。该设计的时钟分配电路允许将多达三个HAPS-64 系统链接或堆叠在一起,从而将系统的容量扩展至 5,400 个ASIC 门。 对于经常可能被带出受控的实验室环境,带到现场和展会展示的原型系统来说,电路板的可靠性是一个重要的问题。HAPS 系统经升级,可采用一个专用监控器 FPGA 来控制电源和时钟的分配,监测电压电平并管理经 Synopsys UMRBus 接口与主机的数据交换。 软硬件混合验证工具

原型系统的未来是什么样的呢?随着像 SCE-MI 这样的联合仿真标准以及像 PCIe 和 Synopsys 的通用多资源总线 (UMRBus) 这样的高性能物理接口的兴起,将用 C/C++/SystemC编写的虚拟原型和硬件原型混合使用现在已具备可行性。这种混合原型方法能够支持设计人员将 IP 与更加丰富多样的模型抽象结合使用,进行验证。HAPS 系统架构就其自身的组织来说,是 SoC 项目的理想选择。在需要观察现实情况下使用的接口时,它可以托管外设子系统。在需要改善数据吞吐能力时,它可以托管硬件执行引擎。 随着像 HAPS 系统这样的商用原型解决方案成为主流验证方法,它们必须遵从标准,以便在现有流程和环境中轻松部署和集成该解决方案。就原型而言,为最大化商用系统的投资回报率,系统必须能够重复使用多年且能够用于各种项目和设计。HAPS 架构的灵活性得益于模块化构思,能够最大程度地减少硬件的使用。这样的模块化原则使HAPS 产品易于理解和构建,并享有开发几乎所有系统原型的自由。稳健可靠的硬件、高度的灵活性、丰富的I/O 连接功能,加上大量的现成硬件模块,使 ASIC 设计人员能够轻松构建自己的定制 ASIC 原型。 如需深入了解“原型设计 (designfor-prototyping)”方法,敬请参阅Doug Amos、Austin Lesea 和 René Richter 合著的《基于 FPGA 的原型方法手册》(FPMM) ( http : / /www.synopsys.com/fpmm )。如需了解Synposys HAPS 的更多信息,敬请访问:www.synopsys.com/haps 。 |  /3

/3

/3

/3