|

摘要: 为了实现电控喷油雾化检测快速测量和处理大量的数据的要求,设计一种基于DSP和FPGA信号控制与实时数据处理系统的通信模块。该通信模块硬件部分主要用来实现开发板GN0204中DSP与FPGA的数据传输,软件部分采用CCStudio3.1和C语言进行编程,能够对传输数据进行控制。最后通过仿真测试,表明该通信模块能够正确的传输数据。

关键词:数字信号处理;可编程门阵列;通信模块;仿真

随着现代测试技术的发展,要求能够对各类微弱信号、高频信号以及复杂信号进行快速、精确的记录和测量,对数据采集系统的采样速率、精度、存储量等提出了越来越高的要求。为了对电控喷油器的喷雾粒度进行精确测试,我们通过充分利用数字信号处理器(Digital Sign al Processing,DSP)强大的控制及数字信号处理能力,配合现场可编程门阵列(Field-Programmable Gate Array,FPGA)高速灵活的数字逻辑电路实现能力,提出一种基于DSP+FPC认结构的31路微电流信号的采集与实时处理系统来对喷雾粒度进行精确测试。

FPGA和DSP处理器具有截然不同的架构。在一种器件上非常有效的算法,在另一种器件上却可能效率非常低。如果目标应用要求大量的并行处理或最大的多通道流量,那么单纯基于DSP处理器的硬件系统就可能需要更大的面积、成本或功耗。一个FPGA协处理器仅在一个器件上就能提供多达550个并行乘法和累加运算,从而以较少的器件和较低的功耗为许多应用提供同样的性能。尽管FPGA在处理大量并行数据方面出类拔萃,但对于定期系数更新、决策控制任务或高速串行数学运算这类任务来说,它们的优化程度比不上DSP处理器。因此,FPGA和DSP处理器的结合为广泛的应用提供了制胜的解决方案。

FPGA和DSP各有特点,在实际系统中经常分工不同的角色。随着大规模可编程器件的发展,采用DSP+FPGA结构的信号处理系统显示出了其优越性,正逐步得到重视。FPGA是在专用ASIC的基础上发展起来的,它克服了专用ASIC不够灵活的缺点,与其他中小规模集成电路相比。其优点主要在于它有很强的灵活性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改和维护很方便,而且在大批量应用时,可降低成本。DSP+FPGA结构最大的特点是结构灵活,有较强的通用性,适于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统易于维护和扩展,适合于实时信号处理。

现在,数字信号处理器(DSP)正越来越多地应用到各种场合,大多数情况下,模拟信号通过A/D转换后,转成高速的数字信号发送给FPGA,经过缓冲FPGA向DSP传送数据,在DSP中进行核心算法的处理后,再把信号发回给FPGA,通过FPGA把发回的信号进行逻辑组合后通过D/A转换成模拟信号输出。可见,FPGA和DSP的通信是数据传输的关键。

1 DSP与FPGA相关原理和外设

本实验所用的是 TMS320C6713系列DSP芯片和ALTERA Cyclone II系列FPGA芯片。FPGA通过DSP的EMIF接口,在DSP的EDMA控制下与DSP进行数据传输。因此,DSP与FPGA的相关原理和DSP的EMIF接口的结构和各端口的功能需要简单的了解。

EMIF是外部存储器和TMS320C6713片内单元间的接口。CPU访问片外存储器时必须通过EMIF,EMIF接口由一组存储器映射的寄存器进行控制与维护,包括配置各个空间的存储器类型和设置读写时序等。

扩展的直接存储器访问控制器(EDMA)主要负责片内的存储器与其他外设之间的数据传输。EDMA进行数据传输时,有2种启动方式:一种是由CPU启动,另一种是由同步事件触发。每一个EDMA通道的启动是相互独立的。

FPGA分为两种:基于查找表的FPGA和基于乘积项的FPGA。查找表(Look Up Table,LUT)本质上就是一个RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。基于乘积项的FPGA可分为3块:宏单元(Macrocell)、可编程连线(PIA)和I/O控制块。宏单元是器件的基本结构,由它来实现基本的逻辑功能;可编程连线负责信号传递,连接所有的宏单元;I/O控制块负责输入输出的电气特性控制,比如可以设定集电极开路输出,摆率控制,三态输出等。

2 DSP与FPGA的通信模块设计流程

DSP的软件开发大体有3种方式:第一种是直接编写汇编语言程序进行编译连接;第2种是编写C语言程序,用C语言优化软件进行编译连接;第3种是混合编程模式,程序中既有汇编代码,又含有C语言代码。使用汇编语言开发程序的设计人员必须熟悉DSP芯片的内部结构。相比C语言,汇编语言开发程序要繁琐的多,但是汇编程序执行起来更加高效。所以对于耗时较大的算法或在实时性要求较高的场合最好用汇编语言开发程序,而在DSP应用较为复杂而实时性要求较低的场合可以用C语言进行开发。这样,既满足了系统的实时性要求,又加快了程序开发的进度。最灵活的方法还是采用混合编程模式开发DSP的用户程序。

FPGA的常用设计方法包括“自顶向下”和“自下而上”,目前大规模FPGA设计一般选择“自顶向下”的设计方法。所谓“自顶向下”设计方法,简单地说,就是采用可完全独立于芯片厂商及其产品结构的描述语言,在功能级对设计产品进行定义,并结合功能仿真技术,以确保设计的正确性,在功能定义完成后,利用逻辑综合技术,把功能描述转换成某一具体结构芯片的网表文件,输出给厂商的布局布线器进行布局布线。布局布线结果还可返回同一仿真器,进行包括功能和时序的后验证,以保证布局布线所带来的门延时和线延时不会影响设计的性能。

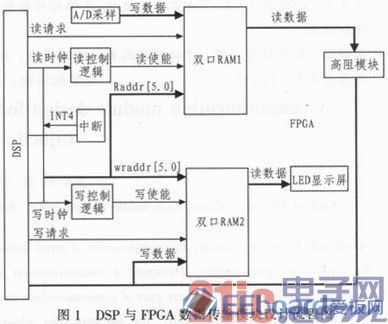

基于DSP的FPGA通信模块设计流程如图1所示。首先在FPGA中创建双口RAMl和RAM2,A/D采样的数据传送到RAMl中,然后RAM1中的数据经过EMIF被读入到DSP中进行实时处理运算,处理后的结果数据在经过EMIF写入到RAM2中,RAM2可以外接LED显示屏显示处理运算结果。在此过程中,RAM1和RAM2共用地址总线和数据总线,在RAM1读和RAM2写数据总线之间插入高阻模块,以防止数据总线冲突。

3 通信模块软件实现

在高速数据采集和处理系统中,随着采样数据量的增大及信息处理任务的增加,对数据传送的要求也越来越高。在系统或模块间如果没有能够高速传送数据的接口,则在数据传送时极易造成瓶颈堵塞现象,从而影响整个系统对数据的处理能力。所以,高速并行数据接口的研制在信息处理系统中占有非常重要的地位。利用高性能双口RAM能够方便地构成各种工作方式的高速数据传送接口,不管是在并行处理网络中的数据共享,还是在流水方式中的高速数据传送中,高性能双口RAM都发挥着重要作用,从而保证数据通路的畅通。创建双口RAM的方法是直接在QuartusII中的MegaWizard Plug-In Manager中创建,如图2(a)和2(b)所示。

RAM1和RAM2都是有一个读端口和一个写端口,存储大小为6432位,数据总线和地址总线都是32位,独立的写时钟和读时钟。不同的是RAM1中导入了初始存储内容(./0517.hex)。

0517.hex中的部分内容如下:

:04000000C000002AD2

:040001000000004487

:040002000000006496

:040003000000008871

:04000400000C008048

:04000500000000D91E

:040006000000102F3

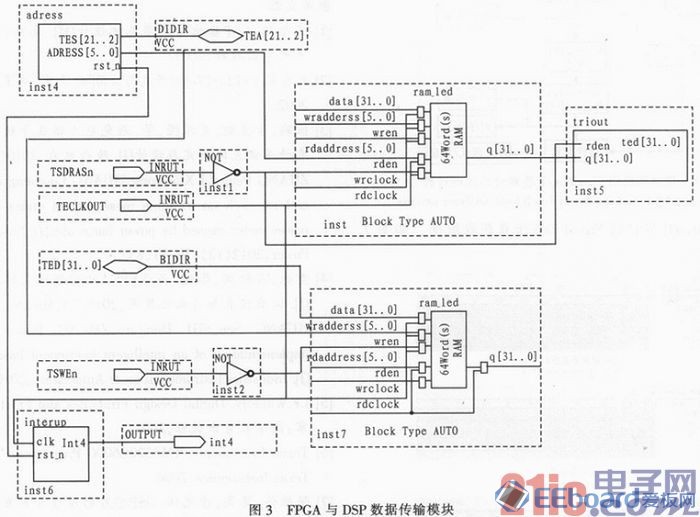

在QuartusII中用原理图的形式创建FPGA与DSP数据传输模块,如图3所示。

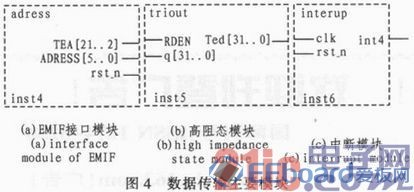

主要的功能模块:1)EMIF接口模块,如图4(a)所示,该功能模块为DSP与FPGA中的双口RAM进行数据传输提供地址和数据总线。2)高阻态功能模块如图4(b)所示,该模块的主要功能是防止总线冲突。3)中断功能模块如图4(c)所示,该功能模块为时钟中断,负责双口RAM读和写的时间控制。

本论文中应用CCStudi03.1集成开发环境并结合C语言编写DSP与FPGA的数据传输的代码。编写流程如图5所示。

4 数据传输验证

随着FPGA设计任务复杂性的不断提高,FPGA设计调试工作的难度也越来越大,在设计验证中投入的时间和花费也会不断增加。为了让产品更快投入市场,设计者必须尽可能减少设计验证时间,这就需要一套功能强大且容易使用的验证工具。Ahera SignalTapⅡ逻辑分析仪可以用来对Altera FPGA内部信号状态进行评估,帮助设计者很快发现设计中存在问题的原因。QuartusⅡ软件中的SignalTapⅡ逻辑分析仪是非插入式的,可升级,易于操作。SignalTapⅡ逻辑分析仪允许设计者在设计中用探针的方式探查内部信号状态,帮助设计者调试FPGA设计。

在设计中嵌入SignalTapⅡ逻辑分析仪有两种方法:第一种方法是建立一个SignalTapⅡ文件(.stp),然后定义STP文件的详细内容;第二种方法是用MegaWizard Plug-InManager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。图6给出用这两种方法建立和使用SignalTapⅡ逻辑分析仪的过程。

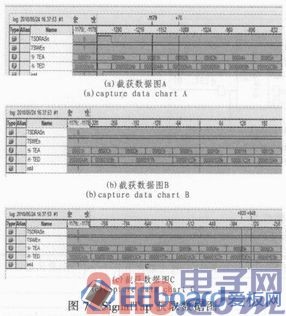

用QuartusII提供的Signal Tap仿真获取数据,如图7所示。

由SignalTap截获的数据图和RAM1中存储的初始值对比可知,两者之间的数值完全符合,由此可知DSP与FPGA的通信模块能够正常通信。

5 结论

文中设计了一种DSP和FFGA数据传输的通信模块,通过Quartus II上完成了FPGA对数据采集系统的时序控制的设计,利用C语言编写DSP与FPGA之间的通信控制代码,应用Quartus II中的Signal Tap功能验证了DSP与FPGA之间数据传输的正确性,证明该通信模块能够实验电控喷油雾化检测快速测量和处理大量的数据的要求。 |  /3

/3

/3

/3