赛题一:RISC-V 仿真并加速验证小系统设计

需要的环境:(点击蓝色字体查看)

题目要求和评分点:

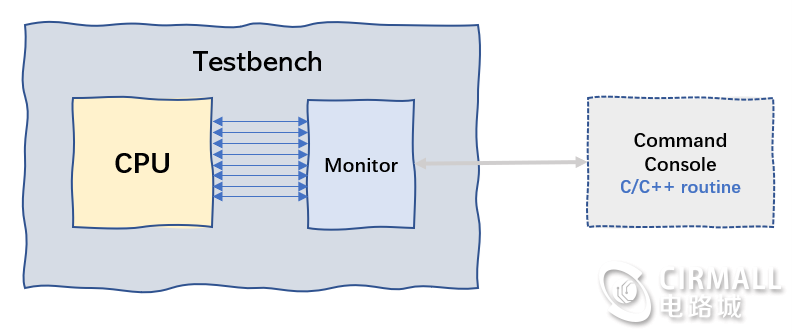

本系统分为4个部分

1. Open-source CPU IP Core

2. 使用RTL 设计Monitor 单元

3. Testbench

4. 命令控制台(C/C++)

设计任务:

1. (30% ) 仿真CPU功能(不包括 Monitor 单元),具体要求如下:

- 在CPU上仿真运行操作系统,系统不限。(15%,使用EPIC-sim 工具20%)

- 显示并打印系统启动过程中的信息(Message)(5%)

- 在系统运行C程序打印“Hello world!” (5%)

2. (30%) 系统Monitor RTL设计

- 获取CPU IP Core 所有 registers 信息,包括hierarchy 路径信息(10%)

示例:cpu. u_e203_ifu. u_e203_ifu_ifetch. u_e203_ifu_litebpu. rs1xn_rdrf_dfflrs. qout_r

- 设计Monitor 单元 ,实现对CPU core中所有Registers 的 monitor,具体的操作如下:(20%)

A.通过控制台输入带有Hierarchy path信息查询 对应 register的值

B.通过控制台输入命令修改带有Hierarchy path信息的register的值

C.通过控制台输入命令查询不同register 逻辑组合运算。

示例如下:cpu. u_e203_ifu. u_e203_ifu_ifetch. data1 & cpu. u_e203_ifu.data2 | cpu. u_e203_ifu. u_e203_ifu_ifetch. data0 ^ cpu. u_e203_ifu.data3&! u_e203_ifu_ifetch. data0 ^ cpu. u_e203_ifu.data3

3. (40%) 命令控制台设计

- 接受命令行输入,查询 对应hierarchy信息的寄存器值。示例如下:(10%)Read cpu. u_e203_ifu. u_e203_ifu_ifetch. u_e203_ifu_litebpu. rs1xn_rdrf_dfflrs. qout_r

- 实现 对应hierarchy信息的寄存器值的修改。示例如下:(10%)write cpu. u_e203_ifu. u_e203_ifu_ifetch. u_e203_ifu_litebpu. rs1xn_rdrf_dfflrs. qout_r 12

- 实现对不同register 逻辑组合运算结果的查询

- 与Simulator 通信,完成上述命令与testbench的交互通信 (20%)

示例:使用DPI-C ,VPI ,PLI等接口或者其他方案。

4. 附加题(50%):生成bitstream,将CPU Core+ Monitor 移植到XILINX FPGA 上(开发平台不限,需要合理选定平台),并设计硬件(RTL)人机交互接口。

已完成前三项设计任务后可继续选择完成附加题,完成附加题优胜概率更高。

最终输出要求: 1. 详细的设计报告,包括FPGA选型报告(20%) 2. RTL综合成功,并给出综合结果(Utilization 报告)(10%) 3. 设计人机交互单元。示例:Uart 或者 Ethernet (20%) 人机交互接口包括FPGA 可实现 RTL 单元和C/C++ driver 4. 生成FPGA 可下载bitstream,并给出Timing 分析报告(10%)

赛题二:纠错编解码算法实现和验证

描述及要求:

1. Verilog实现信道纠错编解码.

2. 编码端,5个通道数据经过编码变为7个通道,每个通道数据位宽8bit.

3. 解码端,要求7个通道中任意损坏一个或两个通道,通过解码恢复出编码前的5通道原始数据.

4. 检测功能不做要求,能实现最好.

评审得分点:

1.功能正确实现;

2.对于模块的面积、性能和功耗优化力度越大,得分越高

3.有对功能验证的完备性分析。功能验证列表越完备,测试覆盖越全面,得分越高

4.在满足同等验证目的的前提下,验证方案越简洁越智能,分数越高;

5.验证手段越多样化,分数越高。如采用断言等。

输出要求:

1.详细设计文档和逻辑代码;

2.有验证的用例和波形截图。

3.有验证方案详细文档。包括验证框架图,功能点列表,测试用例,测试结果,验证质量分析等。

芯华章业专项奖 奖项设置:

一等奖(2队): 人民币10000元

二等奖(4队): 人民币5000元

赛题咨询邮箱:mingkec@x-epic.com

*企业命题最终解释权归芯华章科技股份有限公司所有

|  /2

/2

/2

/2