|

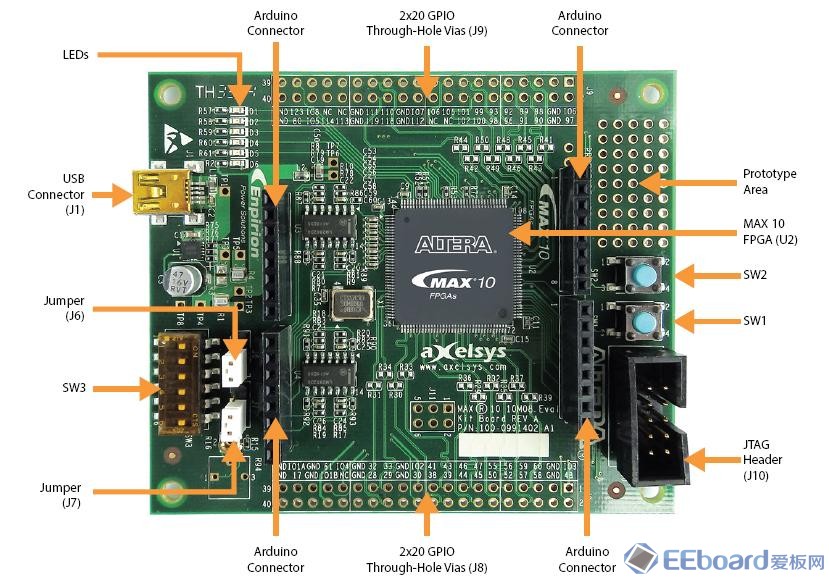

1初识 1.1 评估板全貌

主要包括: 1)MAX 10 FPGA 10M08SAE144C8G芯片(U2):包含8000逻辑单元(LE),378Kb M9K存储器,1376Kb闪存,1个1MSPS 12位A/D转换器等,采用单电源供电,144 引脚 EQFP封装。 2)FPGA配置电路 JTAG Header(J10):用于下载电缆编程 (POF) 或者配置 (SOF) 的 JTAG 插头。 3)时钟电路(X1):50 MHz 单端外部振荡器时钟源。 4)通用I/O (J8 、J9):40个GPIO,可配置。 5)Arduino 插头(J2、J3、J4、J5):14个Arduino I/O,用于接收 UNO R3 兼容外插。 6)5个红色LED灯(D1、D2、D3、D4、D5):用户定义。 7)1个绿色LED灯(D6):显示通过USB电缆上电。 8)按钮和DIP开关(SW1、SW2、SW3):SW1器件复位按纽,SW2重新配置按纽。 9)USB 连接器(J1):通过USB电缆给扳子上电。 10)跳接器(J6、J7) 11)电位计(R94)

1.2 评估板主要功能

1)面向10M08SAE144C8G,144-EQFP FPGA 的开发设计。 2)测量 FPGA 功耗 (VCC_CORE 和 VCC_IO)。 3)实现不同 I/O 电压之间的桥接。 4)对 FPGA 的 NOR 闪存进行读写操作。 5)使用 FPGA 的模数转换器嵌入式模块来测量输入模拟信号。 6)通过 Arduino UNO R3 连接器或者直通过孔实现与外部功能和器件的链接。 7)重新使用套件的 PCB 电路板和原理图,作为您设计的模型。

2 准备工作 2.1 通过USB电缆连接PC和J1,给评估板上电。正确上电时,预设的LED灯D1~D5,每隔1s闪烁。 2.2 安装Quartus II 14.1和MAX10器件文件,以及 USB-Blaster 驱动。 2.3拿评估板时需防止静电,存储温度为-40℃ ~100℃,工作温度为0℃~85℃。 2.4 SW3 DIP开关,6个都默认为开的位置,1~5用户定义,6为BOOT_SEL,用于选择CFM0、CFM1、C***。 2.5 跳接器J6默认连接到GND,PIN1和PIN2短接时为8通道Arduino 插头模拟输入。 2.6 跳接器J7默认连接到电位计,PIN1和PIN2短接时为7通道Arduino 插头为模拟输入。

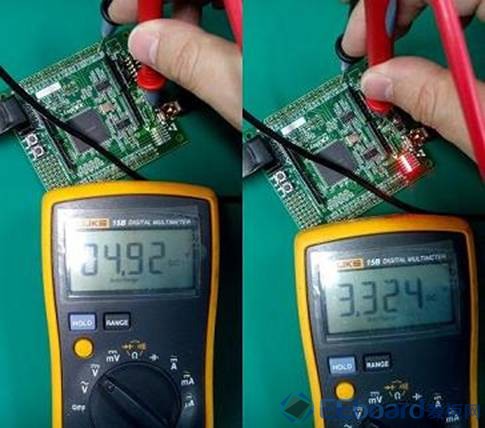

3小试牛刀 3.1 硬件测试 评估板上有多个测试点,测试点TP7,TP8,TP9是GND,测试点TP1电压值为4.92V,是评估板输入电压,TP6电压值为3.324V,是FPGA的供电电压。

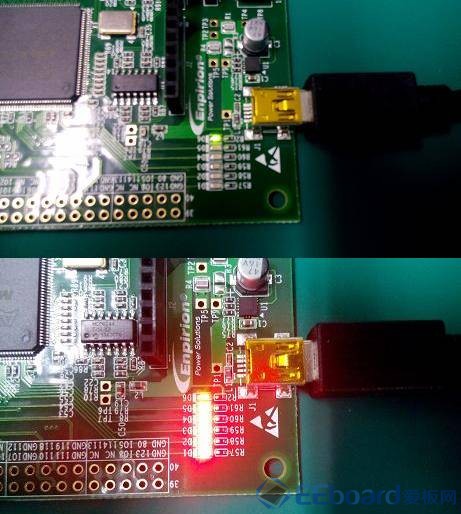

3.2 FPGA设计-LED Flash 根据参考设计文件,在Quartus II 14.1中导入运行LED_Flash.par。该程序功能为评估板上电时LED1~LED5每秒闪烁一次。根据设计方法,说一下设计流程。 先编写程序设计文件LED_Flash_all.V。 module LED_Flash_all( input clk, output LED1, output LED2, output LED3, output LED4, output LED5 );

reg[15:0] div_cntr1; reg[9:0] div_cntr2; reg dec_cntr; reg half_sec_pulse; initial begin div_cntr1 = 0; div_cntr2 = 0; dec_cntr = 0; end always@(posedge clk) begin div_cntr1 <= div_cntr1 + 1; if (div_cntr1 == 0) if (div_cntr2 == 762) begin div_cntr2 <= 0; half_sec_pulse <= 1; end else div_cntr2 <= div_cntr2 + 1; else half_sec_pulse <= 0; if (half_sec_pulse == 1) dec_cntr <= !dec_cntr; end

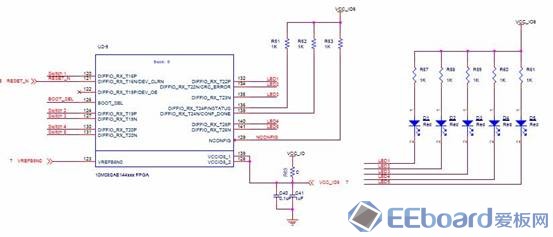

assign LED1 = dec_cntr ; assign LED2 = dec_cntr ; assign LED3 = dec_cntr ; assign LED4 = dec_cntr; assign LED5 = dec_cntr ; endmodule 编译该程序文件,功能仿真与时序仿真,引脚分配锁定,再通过USB Blaster 下载程序。 硬件原理图:

程序运行效果图:

3.3 片上ADC调试 10M08SAE144C8G上有一个单电源,12bit的ADC1,输入电压范围0~2.5V,1LSB=2.5V/4096=610.35uV。 设计步骤:1)建造ALTPLL IP核;2)建造ADC IP核;3)连接ALTPLL IP核和ADC IP核;4)创建 ADC Avalon slave界面,启动ADC。 ADC的图形程序:

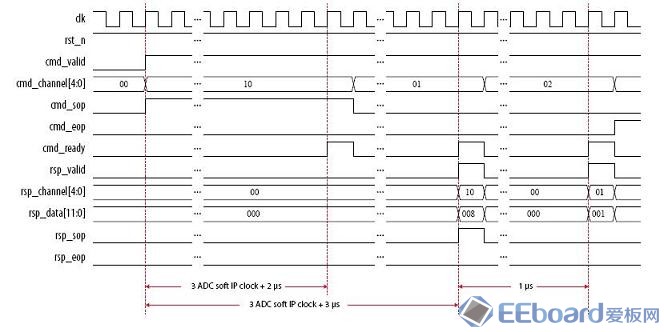

ADC时序图:

调试中ing

4 使用心得 4.1 面向10M08S的FPGA资源丰富,易学易用,简单使用。 4.2 高集成度,集成了双配置闪存、ADC、DSP、DDR3外部存储器接口以及软核Nios II处理器等功能,实现了瞬时配置、失效安全更新、系统监视和系统控制等多种系统功能。并且功耗低。 4.3 集成的模拟模块ADC和温度检测二极管,可以用在需要系统监视的应用中,如温度控制和触摸屏人机接口控制等。 4.4为嵌入式开发人员提供了单芯片、完全可配置的瞬时接通处理器子系统,可用最低的系统成本实现高效的复杂控制系统管理。集成的软核Nios II嵌入式处理器,主频最高200MHz,有着更小的引脚布局,不需要外部RAM或者存储。 4.5采用嵌入式闪存集成方式,实现闪存双配置,一个闪存模块指定用于更新镜像,而另一个模块保留用于“安全”工厂镜像,在镜像间动态切换,降低系统成本和系统风险,其瞬时接通配置和上电排序功能提高了系统管理效率。 4.6 目标市场主要包括工业应用(机器人控制、机器视觉、电机控制等)、汽车应用(信息娱乐、辅助驾驶、电动汽车等)和通信、计算与存储应用等。 原文:http://group.ednchina.com/GROUP_ ... 3840_5000022533.HTM

|  /2

/2

/2

/2