本帖最后由 6100308094 于 2016-3-3 00:21 编辑

我的0v7670还没有寄到。。。先研究着吧。 之前在弄HDMI的I2c配置的时候,就用到了这个东西,今天就写出来吧。可能对初学者有用,有时候我们在signaltap下没办法观察到一些reg和wire变量,因为QII把它给综合掉了,我们可以通过语法,让QII不把它综合掉,以下面为例: 以这个状态机的state为例, - <font face="Tahoma" size="3">//I2C Timing state Parameter

- localparam I2C_IDLE = 4'd0;

- //Write I2C: {ID_Address, REG_Address, W_REG_Data}

- localparam I2C_WR_START = 4'd1;

- localparam I2C_WR_IDADDR = 4'd2;

- localparam I2C_WR_ACK1 = 4'd3;

- localparam I2C_WR_REGADDR = 4'd4;

- localparam I2C_WR_ACK2 = 4'd5;

- localparam I2C_WR_REGDATA = 4'd6;

- localparam I2C_WR_ACK3 = 4'd7;

- localparam I2C_WR_STOP = 4'd8;

-

- reg [7:0] data;

- reg [3:0] state;</font>

找不到state,将上面reg [3:0] state;改为reg [3:0] state/* synthesis preserve */; 请注意,上面格式不要错了, 不能是reg [3:0] state;/* synthesis preserve */

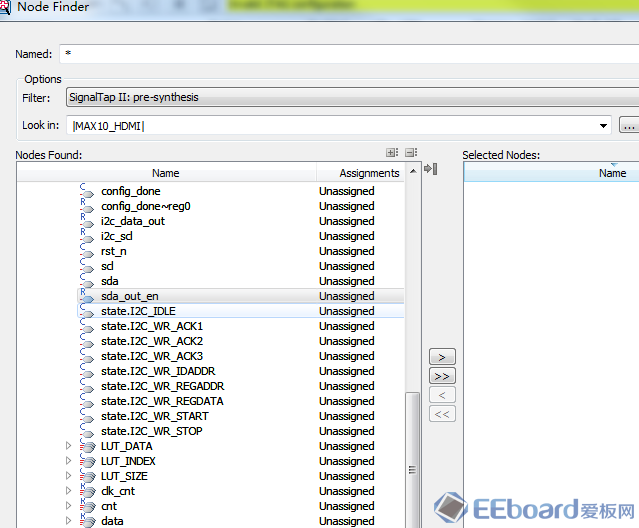

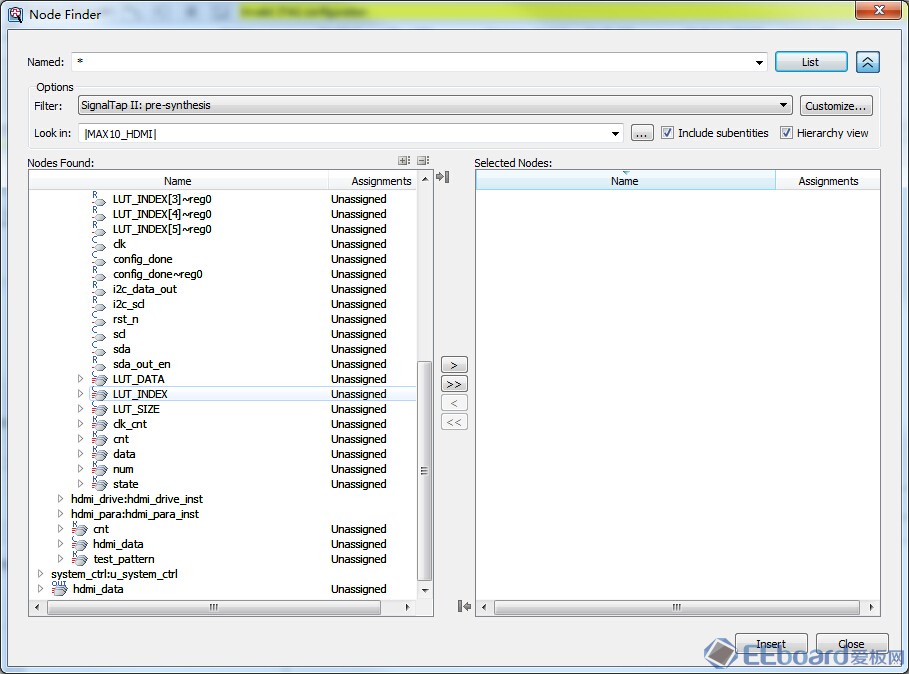

编译,在打开signaltap,

可以看到出现了state变量了,然后就可以添加state,进行观察了。

对于reg主要有以下两种:如果一种不行,就换另外一个吧 /*synthesis preserve*/ 避免Quartus II将reg优化为常数,或者合并重复的reg /*synthesis noprune*/ Quartus II优化掉没output的reg 对于wire型,主要用keep,这里不验证了 wire[3:0] Cnt /*synthesis keep*/; 当然,上面还有其他的形式可以达到同样的效果,大家可以去尝试,希望对大家有用。

|  /2

/2

/2

/2