碳化硅MOSFET四脚封装(典型如TO-247-4或类似封装)中将Driver Source和Gate引脚特意设计得更细,这是一个精妙的工程优化,其好处和设计意图主要集中在 “增强开关性能”和“提高系统可靠性” 上。

简单来说,故意将驱动回路(Kelvin源极)的引脚做细,是为了引入一个可控的、微小的寄生电感,从而隔离高频驱动回路和主功率回路,抑制有害的栅极振荡和电压尖峰。

(在实际设计中遇到栅极振荡或者EMI问题,想通过封装设计来缓解。得联系到驱动回路和功率回路分离的重要性,以及如何通过引脚优化减少寄生参数的影响。

比如开关损耗大或者管子容易坏,所以寻求更稳定的方案。需要强调变细引脚如何提升可靠性,降低设计难度,同时提醒虽然好处多,但驱动设计得配合,比如可能需要更强的栅极驱动能力。

最后得总结,这种设计是为了应对SiC的高频特性,帮助用户实现更高效率和更紧凑的设计,满足行业趋势。得确保解释既专业又易懂,让用户明白这不是缺陷而是精心优化的结果。)

核心原理:分离驱动回路与功率回路

在传统的三脚封装中,源极引脚同时承担着大功率电流回路和驱动信号参考地的双重角色。大电流在源极引脚寄生电感上会产生快速变化的电压噪声,这个噪声会直接叠加到栅极驱动信号上,导致:

栅极振荡:引起误导通或关断不稳定。

开关波形振铃:增加开关损耗和EMI。

驱动电压不稳定:影响开关速度的一致性。

四脚封装的核心理念就是 “开尔文连接”:

功率源极:连接芯片的源极焊盘,承载主功率电流,路径宽、寄生电感小。

驱动源极:通过单独的键合线连接到芯片源极,仅作为驱动芯片的电压参考地,几乎不流过主功率电流。

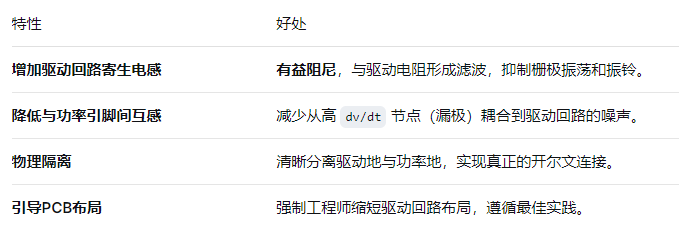

驱动源极引脚变细的具体好处:

构建一个“阻尼器”或“滤波器”

更细的引脚意味着其寄生电感会比粗壮的主功率引脚更大。

这个串联在驱动回路中的小电感(连同走线电感),与栅极驱动电阻、MOSFET的输入电容(Ciss)共同构成了一个低通滤波网络或阻尼网络。

它可以有效衰减从主功率回路耦合到驱动回路的高频噪声和振铃,使栅极电压波形更干净、更稳定。

物理上隔离高频干扰路径

大功率开关的 di/dt 和 dv/dt 非常高,会在功率回路寄生电感上产生巨大的干扰电压。

驱动源极引脚变细,其物理截面积小,与相邻引脚(如漏极)的互感也相对更小。这降低了从高 dv/dt 节点(如漏极)通过互感耦合到驱动回路的干扰。

优化布局,强制设计者关注驱动回路

细引脚在物理上提醒和“强迫”PCB设计工程师必须将驱动回路设计得尽可能短、紧凑且面积小。

一个面积小、环路电感低的驱动回路,自身抵抗外部干扰的能力就强。如果设计者试图用长走线连接这个细引脚,其寄生电感会变得很大,可能导致驱动不稳定,这反过来促使设计者遵循最佳实践。

成本与性能的平衡

在封装内部,驱动源极的键合线通常也比主功率的键合线更细、更少。外部引脚变细与之匹配,是合理的设计。

在满足电流能力(驱动源极电流仅为栅极充放电电流,很小)的前提下,细引脚节省了材料,是一种以巧妙设计提升性能而非堆砌材料的方案。

需要澄清和注意的要点:

目标不是“零电感”:对于功率回路,我们追求尽可能低的寄生电感。但对于独立的驱动回路,引入一个可控的、小值的串联电感往往是有益的,它可以起到阻尼作用。

不是越细越好:引脚需要保证足够的机械强度和承载栅极驱动电流(通常小于2A峰值)的能力。变细是在满足这些前提下的优化。

对驱动设计的影响:由于驱动回路总电感(包括引脚电感)的存在,会略微减缓栅极的开关速度。但这通常是可以接受的,因为换取的是稳定性和可靠性。在极端追求开关速度的设计中,需要综合考虑这个影响。

总结

芯耀

芯耀

2560

2560