大功率三电平应用中 3.3kVSiC MOSFET和IGBT的混合应用问题,针对外管高频、内管低频的调制策略中不同箱位管脉冲时序对三电平有源中点箱位(ANPC)拓扑换流路径、开关损耗以及开关特性等关键因素的影响开展分析,实验验证了不同箱位管脉冲时序对SiC MOSFET和IGBT的动态特性和开关损耗的影响。

SiC MOSFET 模块由于其低开关损耗特性、较 快的开关速度、高耐压、高温稳定性的特点[1,在 高压大功率变流器领域具有显著优势,然而由于 其成本和可靠性问题,目前主流产品仍以IGBT 应 用为主。随着三电平拓扑和SiC 应用技术在轨道 交通领域逐渐受到更多关注I²-51,在兼顾成本和高 频、高功率密度设计要求的同时,使得 SiC 和 Si 混合应用具有较好的发展前景。

在 ANPC 拓扑中由于箱位管的存在,使得调制策略存在更多自由度,而目前最为常见的两种调制策略分别为内管低频、外管和箔位管高频的PWM1 策略和内管高频、箱位管和外管低频的PWM2策略。PWM1策略由于其所有开关切换都 是最小换流路径的特性,在高压大功率应用中更为常见,因此本文以 PWM1 策略的ANPC 拓扑在 混合SiC应用中的问题开展研究。

SiC MOSFET 和 IGBT 的开关特性存在较大差异,上述两种器件混合应用时其各自的开关过程将会相互影响。而通常在混合SiC 应用中SiC 的开关损耗占主导部分,因此会对SiC MOSFET的开关损耗造成较大影响,影响整体效率和性能。3.3 kV Si IGBT 模块中二极管芯片存在较为显著的反向恢复过程6,在特殊的换流路径中,会导致 SiC MOSFET 芯片开通过程中叠加IGBT 反向恢复 电流。因此,在混合SiC 应用中需要针对Si 与SiC 的切换过程进行分析。

原理与设计

ANPC三电平拓扑比二极管中点箔位型(NPC)三电平拓扑多两个箱位管开关器件,使得ANPC 拓扑的调制策略有更多种可能性。在NPC拓扑中,为了解决内管和外管的均压问题,通常会采取在两个箱位二极管两端并联电阻,如图1a中的Ra所示。均压的效果取决于电阻的阻值,阻值越小均压效果越好,但会增加变流器系统的整体损耗。在ANPC拓扑中能够通过箱位管的主动开关解决该 问题,而箔位管开关的时刻不同将会导致换流路径的变化,影响开关器件的关断过电压。在进行驱动电阻配置时,通常会考虑过电压对器件可靠性的影响,从而进一步影响变流器整体损耗。因此,需 要对不同箔位管调制策略下的换流路径开展分析。

换流分析

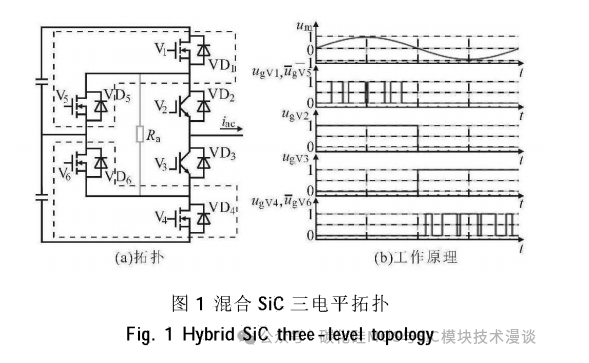

图1a 为混合SiC三电平ANPC拓扑图,外管V₁ 和箱位管V₅ 采用SiCMOSFET,内 管V₂ 采用Si IGBT。其中上半桥臂中V₁和V₅为3300V/750 A的 SiCMOSFET半桥模块,V₂ 为3300V/1000A的 IGBT模块,下半桥臂与之类似。图1b为 PWM1策略下ANPC拓扑的基本工作原理。当调制波um>0 时 ,V₂ 常开 ,V₃,V₄,V₆ 关断 ,V₁ 和V₅ 互补开关, 当 um<0 时,与之相反。当采用这种调制策略时,箱 位管不能实现主动箱位的作用,仍然需要均压电 阻 R, 实现内外管均压。

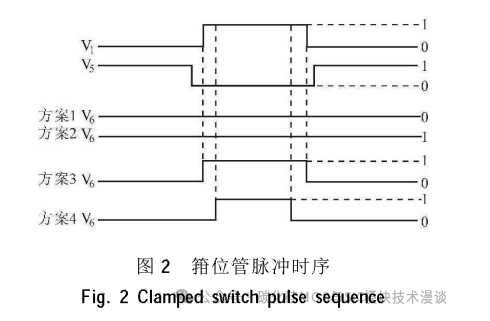

考虑到箔位管的时序逻辑对换流路径的影响,其开关逻辑为:①不进行主动箔位,即当um>0 时,V₆ 始终关断;②当 um>0 时,V₆ 常开;③当um>0 时,V₆ 与V₁ 同时开通、关断;④当um>0 时,V₆ 晚 于 V₁开通,提前于V₁ 关断。图2为箔位管脉冲时序。

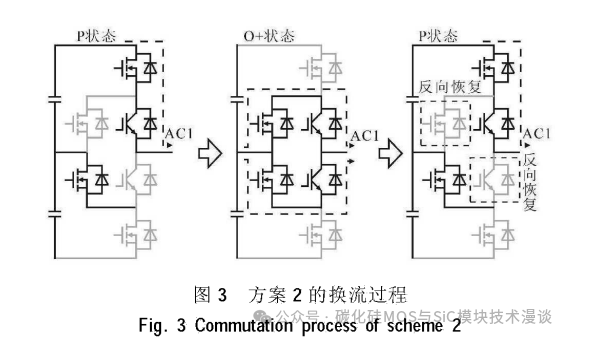

输出电流大于零且um>0 时,4种方案的分析结果如下。图3为方案2的换流过程。

方案 1当输出状态从P状态切换为0+状态时,V₁ 关断,V₂ 保持开通,电流从流过V₁IV₂ 切换至VD₅/V₂当输出状态从0+状态切换至P状态时,V₁开通,V₂保持开通,电流从VD₅/V₂切换至V₁IV₂,此时VD₅发生反向恢复。该方案下只有V₁和VD₅ 之间发生换流。

方案 2 当输出状态从P状态切换为0+状态时,V₁ 关断,V₂ 和 V₆ 保持开通,电流从流过V₁IV₂切换至VD₅/V₂和V₆/VD₃。当输出状态从0+状态切换至P 状态时,V₁开通,V₂ 和V₆ 保持开通,电流从VD₅/V₂ 和V₆/VD₃ 切换至V₁IV₂, 此时VD₅ 和VD₃发生反向恢复。该方案下V₁,VD₅ 和VD₃ 之间发生换流,如图3所示。由于换流过程中VD₅ 和VD₃同时存在反向恢复,因此VD₅ 和VD₃的反向恢复电流之和会叠加至V₁ 的开通过程,从而导致V₁ 的开通损耗增大。

方案3和方案4的换流过程与方案1类似,因此不再赘述。方案4中V₆ 与V₁ 的开关时序相差的时间至少要大于V₁ 的最小脉宽,以保证V₆开通时V₁ 与VD₅ 已经完成电流切换。在方案4的V₆关断后,V₃,V₄ 之间的电位未达到新的平衡状态,若此时关断V₁ 会引起V₁ 的关断电压产生振荡。

输出电流小于零且 um<0 时,4种方案的P 状态 和O+ 状态的电流切换都是发生在 VD₁ 和 V₅ 之间 ,SiC MOSFET 的开关损耗不会受到影响。此外, 调制波um<0 与 um>0 的换流分析过程类似。

损耗计算

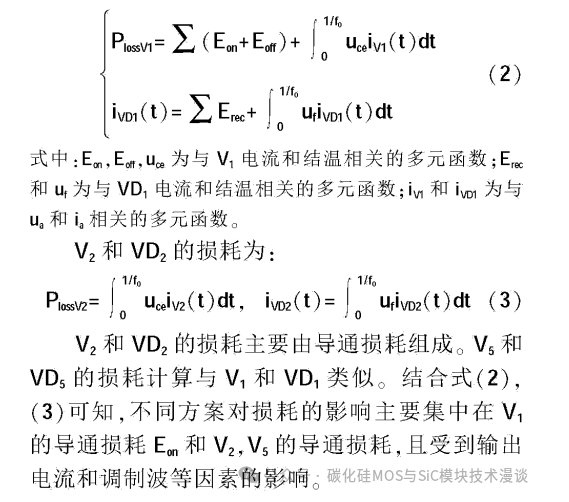

由第2 . 1节中分析可知,方案2会在输出电 流大于零且 um>0 和输出电流小于零且 um<0 的 工 况下增加SiC MOSFET的开通损耗。考虑以上情 况,混合SiC 三电平拓扑的损耗计算如下。假设输出电流和调制波为:

实 验

通过第2节中的分析可知,箔位管的逻辑不同主要对外管的开关过程有影响,因此本文对不同箔位管逻辑下的外管开关特性进行测试。由于 V₁ 测试过程中SiC 器件的高开关速度引起的共模 干扰过大,因此在实验中选取V₄ 为测试对象。为 了避免上半电容充电从而影响测试结果,实验过 程中将正母排与上半电容断开进行测试。

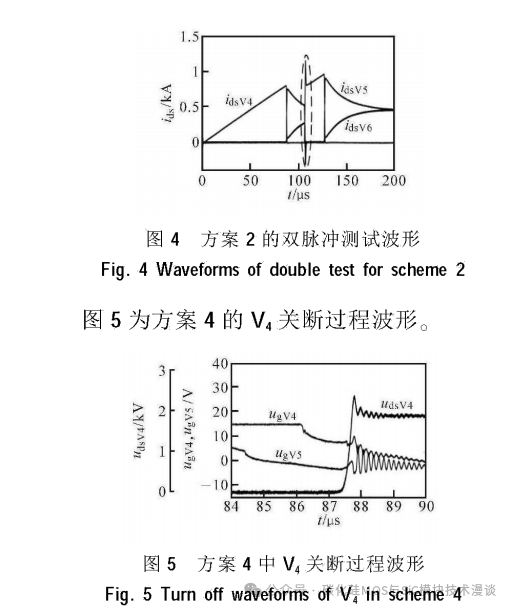

图4为方案2的双脉冲测试波形。可见,当V₄ 关断后,V₅和 V₆ 处于并联状态。当V₄ 再次开通时,VD₆ 和 VD₂ 同时发生反向恢复(图中虚线圈所示)。

当V₄ 关断后,V₄ 的漏源极电压上升至直流电 容电压时其电压产生振荡现象。

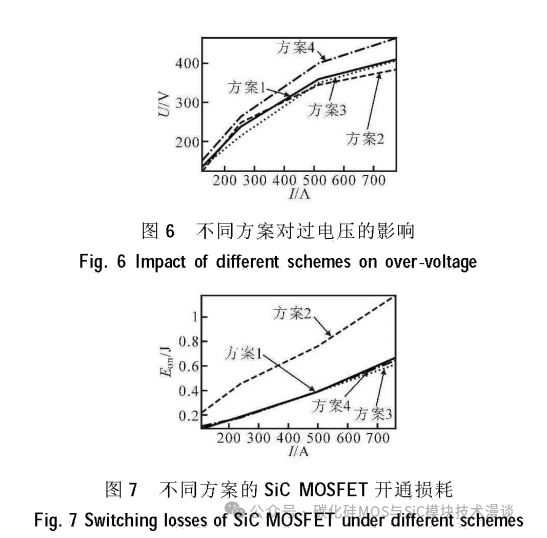

图6和图7分别为不同方案的过电压和损耗特性,方案4关断过电压最大,方案1和方案3接近。方案2由于O+ 状态处于并联,等效换流的电 流仅有其他方案的一半,关断过电压最小。方案1, 3,4的开通损耗基本接近,方案2的开通损耗是其他方案的2倍左右。

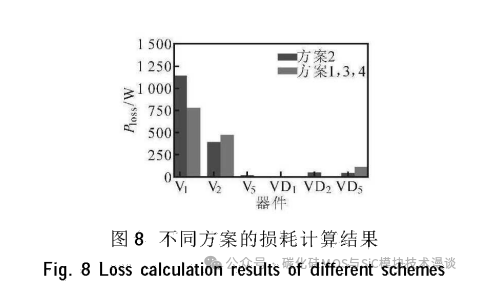

由于方案2在0+状态时存在两条路径,其 0+状态的通态损耗小于其他几种方案,还需要对不同方案的变流器损耗进行量化分析。图8为开 关频率2 kHz, 输出电流有效值500 A,直流电压3600V条件下不同方案的损耗分布图。

结 论

针对3.3 kVSiC MOSFET和IGBT 在ANPC三电平拓扑中混合应用目前存在的问题开展分析,通过实验结果验证了分析结论。综合实验结果和分析结论,从最高效率和可靠性的角度出发,方案3是当前应用背景中的最优解决方案,但是还需通过额外的硬件或者软件设计,保证方案3中外管和箱位管脉冲的同步性。

芯耀

芯耀

2168

2168