最近在与非网的公众号活动中收到了《基于FPGA与RISC-V的嵌入式系统设计》,趁着有空浅读一下,解决部分心中的疑问。

RISC-V,顾名思义,即为“第五代RISC指令集”,是一种基于精简指令集计算机(RISC)原理的开源指令集架构(ISA)。它是由加州大学伯克利分校的研究人员于2010年首次开发的,旨在提供一个免费、可扩展且可定制的指令集,以促进处理器技术的创新和多样性。

RISC-V的指令集是开放的,任何人都可以免费使用,不需要支付专利费或版权费。RISC-V以其模块化设计、可扩展性和简洁性而著称,它允许任何人免费使用和定制,从而降低了处理器设计的门槛,促进了技术的创新,并支持从嵌入式系统到高性能计算等多种应用场景,逐渐成为全球范围内推动自主可控和技术发展的重要力量。

很多人对于RISC-V的概念仅限于:一种不同于ARM的、开源的全新架构。但是RISC-V究竟有什么特点,他和ARM、cisc等架构的主要区别在哪里?作者通过简单的对比说明了这个困扰我多年的问题。

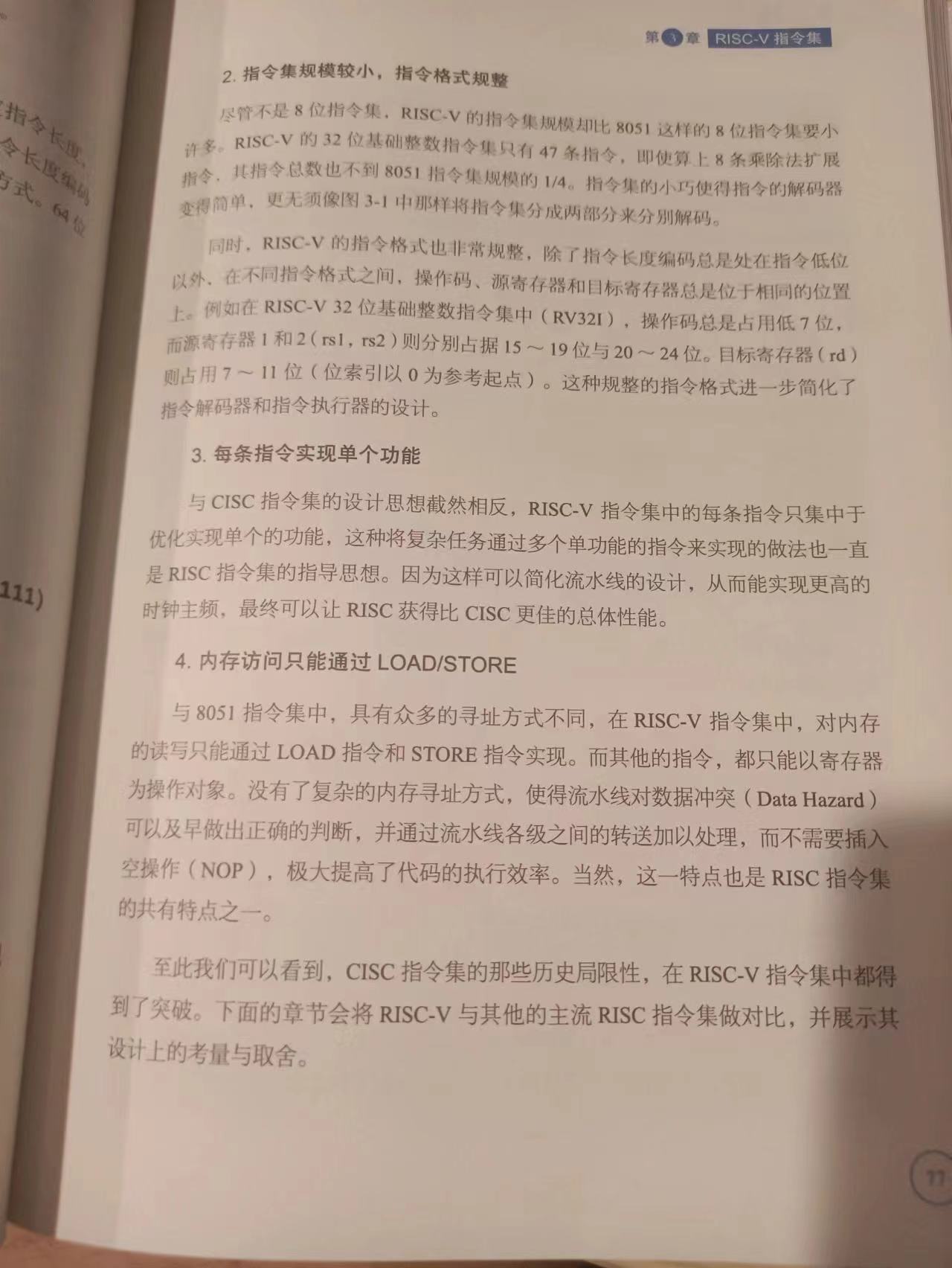

RISC-V和8051架构相比:8051应该是大多数电子相关专业学生所学习的第一款处理器,以寻址方式为例,8051支持立即数寻址/间接寻址/直接寻址/寄存器寻址四种寻址方式(死去的记忆在攻击我)。“这样众多的寻址方式,使得许多指令可以访问内存,导致流水线的数据冲突很难判断,不得不以硬件自动插空以保证数据的正确和完整。这样既消耗了逻辑资源,又降低了流水线效率”(书中摘抄)。但是RISC-V只能通过LOAD指令和STORE指令实现内存的读写,其他指令都只能以寄存器位操作对象,这样不需要插空操作,极大的提高了代码的执行效率。

后面作者花费了大量的篇幅以详尽的介绍了自己的RISC-V SOFT CPU CONTEST获奖作品:PulseRain Reindeer,碍于本人愚钝,请感兴趣的朋友去看书籍原文,或者看下作者的GITHUB开源页:

GitHub - PulseRain/Reindeer: PulseRain Reindeer - RISCV RV32I[M] Soft CPU

感谢与非网为我提供的精美书籍,让我在工作之余GET到又一些接触不到的知识。祝愿与非网越办越好!

芯耀

芯耀

2589

2589

下载ECAD模型

下载ECAD模型