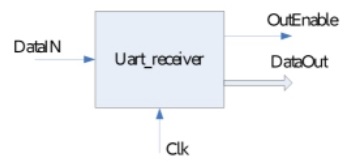

名称:UART接收电路(防毛刺)设计VHDL代码modelsim仿真

软件:modelsim

语言:VHDL

代码功能:

设计一个UART接收电路,其工作原理为

输入输出信号说明:

Datain:输入串行码流,速率为11.52 Kbits/S

CLK 输入时钟,频率为50MHz;

Dataout:输出并行数据信号(8bits宽度)。

电路功能说明:对输入的串行数据码流,用高速的时钟进行采样处理,将异步串行输入的数据流转换为同步的并行数据输出。

1.输入码流 Datain,速率为1152kbts/S;时钟速率是50MHz,当时钟上升沿时进行数据釆样。

2.当 Outenable信号为高时,并行输出数据有效。

3.串行输入数据流是以数据帧的格式输入的;其帧号依次递增。毎帧包含一个起始位、8bits数据位和一个停止为,其示意如下图所示。当无数据输入时,信号线状态保持为高("1")。而数据帧的起始位(Datai)固定为‘0',它标志着一个数据帧的开始;停止位( Datae)固定为1',它标志着一个数据帧的结束。

设计要求:

输入信号时序波形为(8bit数据,高位在前):56H、37H、AOH4BH、FFH。在第一帧数据出现前有一个宽度为500ns的低脉冲毛刺,在第一帧数据的起始位的后半段,有一个宽度为500ns的高电平脉冲毛刺。

2.接收电路能够在毛刺存在的条件下,正确检测岀串行传输数据。

2.在同一个进程中不能有两个' event

3.除 testbench程序外,不能使用 after语句。

提示:

设计一个毛刺计数器,如果出现毛刺则进行计数。如果最后毛刺计数器的计数值高于某个门限,则表明本接收状态出现错误,需要重新搜索接收状态;如果毛刺计数器的值还很小时,就又出现了正确数据,则毛刺计数器清零。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

演示视频:

设计文档:

1. 代码文件

顶层模块

波特率分频模块

滤波模块(去除毛刺)

Uart接收模块

Testbench

仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY filter IS PORT ( clk : IN STD_LOGIC; rst_n : IN STD_LOGIC; signal_in : IN STD_LOGIC; signal_out : OUT STD_LOGIC ); END filter; ARCHITECTURE RTL OF filter IS TYPE state_FSM is (s_idle,s_high,s_high_cnt,s_low,s_low_cnt); signal state:state_FSM; SIGNAL signal_data : STD_LOGIC; SIGNAL cnt : STD_LOGIC_VECTOR(5 DOWNTO 0) := "000000"; BEGIN PROCESS (clk, rst_n) BEGIN IF ((NOT(rst_n)) = '1') THEN cnt <= "000000"; ELSIF (clk'EVENT AND clk = '1') THEN IF (state = s_high_cnt OR state = s_low_cnt) THEN cnt <= cnt + "000001"; ELSE cnt <= "000000"; END IF; END IF; END PROCESS;

点击链接获取代码文件:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=1135

芯耀

芯耀

1124

1124