碳化硅(SiC)MOSFET在开关过程中产生的 CE(Collector-Emitter,即漏-源极)震荡 和 GE(Gate-Emitter,即栅-源极)震荡 是常见的动态问题,主要由以下原因引起:

一、CE震荡(漏-源极电压/电流震荡)

现象:在开关过程中,Vds 和 Id 出现高频衰减振荡。根本原因:寄生电感和寄生电容形成LC谐振电路。

主要原因及对策:

回路寄生电感(关键因素)PCB 走线电感(尤其是功率回路布局不佳)。

直流母线电容的ESL(等效串联电感)。

器件封装电感(源极寄生电感 Ls 影响最大)。

主要来源:

机理:开关瞬间电流变化率(di/dt)极大,在寄生电感上产生感应电压:

对策:

优化布局:尽量减小功率回路面积(采用叠层母排、紧贴式布局)。

对策:

二极管反向恢复(与体二极管或并联二极管相关)

SiC MOSFET体二极管反向恢复电流小,但仍有少量反向恢复电荷(Qrr),可能激发谐振。

对策:优化死区时间,避免体二极管导通(采用软开关或同步整流)。

Coss(输出电容)与Lpar谐振

开关过程中,Coss 与寄生电感在电压突变时谐振。

对策:选择Coss较小的器件,或增加栅极电阻减缓开关速度(但会牺牲效率)。

二、GE震荡(栅-源极电压震荡)

现象:栅极驱动电压Vgs出现高频振荡,可能误触发或损坏器件。根本原因:栅极回路的寄生电感和电容耦合了高频噪声。

主要原因及对策:

米勒电容(Cgd)耦合

机理:开关过程中,Vds急剧变化通过米勒电容(Cgd)注入电流到栅极:

对策:

减小栅极回路电感:使用短而粗的驱动走线,双绞线或同轴电缆。

增加栅极电阻(Rg):可阻尼振荡,但会降低开关速度。

采用开尔文源极连接:将驱动回路与功率源极分开,避免源极寄生电感(Ls)的影响。

对策:

驱动回路寄生电感

在栅极就近串联小电阻(如2-10Ω)阻尼振荡。

驱动路径的寄生电感(包括芯片键合线、PCB走线)与栅极输入电容(Ciss)形成LC谐振。

对策:

共同源极电感(Common Source Inductance, Ls)

关键影响:源极寄生电感(Ls)同时影响功率回路和驱动回路。开关时,Ls上的感应电压会抵消驱动电压,导致Vgs波动。

对策:选择低电感封装的器件(如TO-247-4L,带有独立开尔文源极引脚)。

驱动电路布局不佳

驱动IC靠近MOSFET放置。

使用多层板,驱动走线在内层或采用地平面屏蔽。

驱动回路面积大,易耦合高频磁场噪声。

对策:

驱动IC靠近MOSFET放置。

使用多层板,驱动走线在内层或采用地平面屏蔽。

三、通用抑制措施

优化PCB布局:功率地与驱动地单点连接。

最小化功率回路和驱动回路的寄生电感。

使用合适的栅极驱动参数:必要时采用负压关断(如-5V)防止误触发。

调整栅极电阻(Rgon/Rgoff)平衡开关速度与振荡。

缓冲电路设计:

在漏-源极之间并联RC缓冲电路吸收振荡能量。

器件选型:选择Coss和Cgd较小的器件。

选择低寄生电感的封装(如DFN8×8、TO-247-4L)。

总结

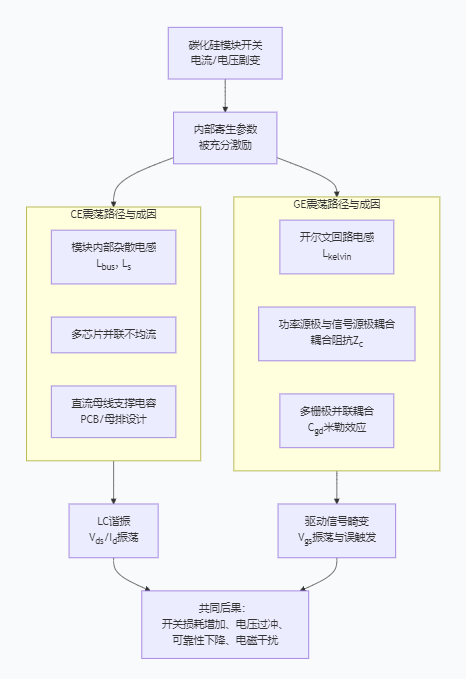

碳化硅模块内部的CE震荡和GE震荡,其根本原理与单管类似,但由于模块内部结构的高度集成、多芯片并联、以及更复杂的内部互连,其寄生参数的形成机理、表现和解决方法有显著不同。

下图清晰地展示了碳化硅模块中寄生参数引发震荡的核心路径与成因:

一、模块特有的CE震荡原因(比单管更复杂)

1. 模块内部杂散电感

这是最主要、最核心的原因。

直流母线杂散电感(LBUS):模块内部的直流正(P)和直流负(N)端子到芯片之间的绑定线、内部铜排/基板走线产生的电感。这是引起关断电压过冲和振荡的元凶。

机理:关断时,极高的 -di/dt 在 LBUS 上感应出尖峰电压

Vspike = LBUS * di/dt。这个尖峰电压与模块的输出电容(Coss)以及外部电容形成LC谐振电路,产生衰减振荡。

模块特点:模块内部的LBUS通常已由设计优化,但远不为零(典型值在几nH到几十nH)。高频SiC开关下,即使很小的LBUS也能引起显著振荡。

2. 多芯片并联的相互作用

模块通常由多个SiC MOSFET芯片并联以实现大电流。

不均流与动态振荡:并联芯片的阈值电压(Vth)、跨导(gfs)、寄生电容(Ciss, Coss, Crss)存在细微差异。在超快开关瞬间,这种差异会被放大,导致芯片间电流分配不均,并可能形成芯片间的电流环流,激发出更高频的振荡模式。

布局不对称:模块内部,距离直流端子或交流端子不同位置的芯片,其回路电感有微小差异。这种不对称的寄生电感会导致各芯片的开关时刻和速度略有不同,从而相互影响,产生振荡。

3. 外部电路设计的放大效应

模块将高功率密度集成在一起,对外部电路的要求更高。

直流母线电容的位置和类型:如果直流支撑电容距离模块端子太远,或使用的是高频特性不佳的电解电容,那么外部回路的寄生电感将与模块内部电感叠加,严重恶化振荡。

PCB/母排设计:连接模块端子的外部母排或PCB的寄生电感是LBUS的直接延伸,必须最小化。

二、模块特有的GE震荡原因(驱动挑战更大)

1. 开尔文源极(Kelvin Source)回路的寄生电感

几乎所有高性能SiC模块都提供独立的开尔文源极引脚(或叫驱动源极、信号源极)。

关键作用:将驱动电流回路与主功率电流回路分开,避免主功率源极寄生电感(Ls)上的感应电压干扰驱动地。

模块特有风险:

内部开尔文连接电感(Lkelvin):模块内部从SiC芯片的源极焊点到开尔源极引脚之间仍然存在一段连接(如细绑定线)。这个电感虽然比主功率电感小,但在极高的dv/dt和di/dt下仍不容忽视。

外部驱动回路电感:从驱动板到模块开尔文引脚的走线电感,如果过长,会与模块的输入电容(Ciss)形成LC谐振,导致栅极振荡。

2. 功率源极与信号源极的耦合

即使在有开尔文源极的情况下,模块内部的功率源极和信号源极最终在芯片层面仍是连接在一起的。极高的dv/dt会通过芯片内部或封装内部的耦合电容,将噪声注入到开尔文回路,导致Vgs出现共模噪声或振荡。

3. 多栅极并联的相互干扰

并联芯片的栅极在模块内部通常是连接在一起的。一个芯片的米勒电容(Cgd)耦合过来的电流,可能会通过共享的栅极路径干扰其他芯片的栅极电压。这种多栅极之间的耦合增加了驱动回路的不稳定性。

三、针对模块的抑制措施(系统性方案)

1. 优化主功率回路布局以抑制CE震荡

使用叠层母排:这是降低外部寄生电感最有效的方法。正负极铜板紧密叠放,中间是绝缘层,使得磁场相互抵消,可将寄生电感降至1-10nH级别。

使用高性能薄膜电容:将低ESL/ESR的薄膜电容(如聚丙烯电容)直接并联在模块的P/N端子上,为高频开关电流提供最近的回路。电解电容仅用于储能。

对称化布局:确保模块的交流输出端子到负载的回路对称、紧凑。

2. 优化栅极驱动设计以抑制GE震荡

驱动板紧贴模块:将驱动板直接安装在模块的驱动引脚上方或用短排线连接,绝对避免长引线。

双脉冲测试法:设计和优化时必须使用。通过观察Vgs和Vds波形来调整参数。

调整驱动参数:

调整栅极电阻(Rg):增加Rg可以阻尼振荡,但会增加开关损耗。可以尝试使用非对称驱动(开通电阻小,关断电阻略大)或多级驱动。

使用有源米勒钳位:防止在关断或桥臂死区时间因米勒效应导致的误导通。

采用负压关断:例如采用+18V/-5V驱动,提供更强的抗干扰能力,防止误触发。

优化RC缓冲电路:在模块的P-N或C-E之间并联RC缓冲电路(snubber),直接吸收振荡能量。这是抑制CE震荡的有效手段,但会增加损耗。需要精确计算和实验调试。

3. 充分利用模块的先进特性

必须使用开尔文源极引脚!并将驱动器的地线与开尔文引脚用最短、最粗的路径连接。

关注模块数据手册的推荐驱动电路和布局指南,厂商通常提供了经过验证的方案。

总结:模块 vs. 单管的核心差异

核心思想:碳化硅模块将高性能和高密度集成在一起,但同时也将寄生参数和相互耦合“锁定”在内部。因此,外部电路(尤其是低电感布局和低电感电容)不再是“优化项”,而是“必需品”。抑制震荡的关键在于为模块提供一个“完美”的外部工作环境,以匹配其内在的高速开关能力。

芯耀

芯耀

1371

1371