绝大多数商用碳化硅MOSFET被设计为不具备雪崩能力,且不应在其数据手册规定的最大额定电压VDSS之外工作。

这与传统的硅基功率MOSFET有根本性的区别。

详细解释与分析:

1. 硅 vs. 碳化硅的设计哲学

硅MOSFET:为了在硅材料上实现低导通电阻Rds(on),通常需要增加芯片面积,这会导致成本上升和开关性能下降。因此,许多硅MOSFET被设计为允许一定程度的雪崩击穿,作为一种“牺牲性能换取的自我保护机制”。当电路中不可避免的感性电压尖峰超过VDSS时,器件通过可控的雪崩效应耗散能量,保护自身不立即损坏。其数据手册中会明确给出“单脉冲雪崩能量 EAS” 和“重复性雪崩额定值”等参数。碳化硅MOSFET:碳化硅材料本身就具有10倍于硅的临界击穿电场强度。这意味着制造商可以用更小的芯片面积、更薄的外延层来实现相同的电压等级和更低的Rds(on) 。这种设计追求的是极致的开关速度、频率和效率。允许雪崩击穿会严重威胁到薄层结构的可靠性。因此,设计原则是:

“绝不击穿,一切过压都是危险的。系统设计必须确保工作电压(包括尖峰)始终低于VDSS

2. 碳化硅MOSFET“缺乏”雪崩能力的具体表现

数据手册中无雪崩额定值:你可以翻看任何一家主流厂商(Wolfspeed, Infineon, ST, ROHM, onsemi等)的SiC MOSFET数据手册,基本找不到EAS这个参数。取而代之的是,在“绝对最大额定值”表格中,VDSS被严格标注,并伴有类似“在任何情况下都不应超过”的警告。

失效模式不同:

体二极管的反向恢复:值得注意的是,SiC MOSFET的体二极管几乎没有反向恢复电荷,但其反向恢复的 di/dt极高。这虽然降低了开关损耗,但也可能加剧桥臂串扰和电压振荡,间接增加了过压风险,需要从系统层面予以抑制。

最终建议

忘记“雪崩”这个词:在设计SiC电路时,请从脑海中移除硅时代的“雪崩能量缓冲”概念。Vdss 是一条绝对不可触碰的高压线。

设计目标:你的设计目标应是——在包括最恶劣工况(如关断最大负载电流、短路保护、高温等)的所有情况下,用示波器测量到的MOSFET引脚上的瞬时Vds峰值,必须始终低于数据手册中的Vdss 并留有足够裕量(如10-20%)。

3.诊断关键:失效后,如果怀疑是过压导致,重点检查功率回路寄生电感和吸收电路的有效性,而不是去查阅一个根本不存在的 EAS参数。碳化硅MOSFET凭借其材料优势,通过取消雪崩能力,换取了更高的性能密度和速度。这并非缺点,而是一种不同的设计哲学,它要求系统设计具有更高的精度和严谨性,尤其需要在降低寄生参数和抑制电压尖峰上投入巨大精力。

碳化硅(SiC)MOSFET由于其材料特性和结构设计,在雪崩能力和高dV/dt导致的失效机理上与传统的硅(Si)MOSFET有显著差异。以下是针对SiC MOSFET这两种失效模式的深入分析。

核心差异:SiC MOSFET的特性

通常不具备雪崩能力:绝大多数商用SiC MOSFET在设计上不保证或不支持重复性雪崩操作。其额定电压 Vdss 是一个绝对最大额定值,而非像部分硅MOS那样有雪崩能量EAS规格。一旦超过,极易损坏。

更高的开关速度:SiC器件开关速度极快(dV/dt可达50-100 V/ns),这使得由高dV/dt引发的寄生效应成为最主要的失效风险之一。

更严格的栅极电压要求:栅氧层更薄,栅极耐受电压(通常±20V~25V)相对硅器件(±30V)更低,对驱动要求更苛刻。

体二极管反向恢复特性不同:SiC MOSFET的体二极管几乎没有反向恢复电荷,但其反向恢复dV/dt极高,可能带来独特的风险。

一、 电压过冲(超越VDSS)导致烧毁

在SiC MOSFET中,这通常不称为“雪崩”,而更准确地称为“过压击穿”。

1. 机理与原因分析:

主要原因:关断电压尖峰:由功率回路寄生电感 Ls极高的关断di/dt共同作用产生。电压尖峰 ΔV=L s×di/dt。SiC的 di/dt极高,即使很小的寄生电感(几个nH)也会产生巨大尖峰。

门极驱动负压不足或不稳定:负压不足或振荡会导致器件在高压下提前微导通或误导通,造成直通短路,瞬间拉高电流和电压,引发连锁击穿。

栅极驱动参考点(Source)电位剧烈振荡:由于源极寄生电感 Lsource的存在,快速变化的漏极电流会在其上产生感应电压Ls=Lsource ×di/dt,这会调制实际加在栅源两极间的电压 VGS,可能导致误导通,进而引发过压击穿。

2. 失效特征:

与硅器件类似,芯片可能局部熔毁,D-S常呈短路。

失效往往发生在开关瞬间,而非稳态。

3. 解决方案:

极致优化PCB布局:核心中的核心。目标是最小化功率回路(特别是开关节点的环路)和驱动回路的寄生电感。使用低感层叠母排、对称布局、大面积接地。

精确设计吸收电路:在直流母线或开关节点的D-S间使用高频薄膜电容构成RCD或RC吸收,钳位电压尖峰。电容必须低ESL。

使用高可靠性负压关断:推荐使用-3V至-5V稳定负压关断,提高抗干扰能力。

选择合适电压等级:在400V母线下,考虑使用750V甚至1200V的SiC MOSFET以提供充足裕量。

二、 高 dV/dt 导致烧毁

这是SiC MOSFET应用中最常见、最棘手的失效模式,机理比硅器件更复杂。

1. 主要机理与原因分析:

a) 米勒效应导致的栅极电压抬升(与硅类似但更严重)

原因:极高的开关节点电压变化率 dV DS /dt 通过米勒电容 CGD 产生更大的位移电流 i=CGD×dV DS/dt。如果栅极驱动关断阻抗不够低,该电流会在栅极电阻或驱动回路寄生电感上产生压降,使VGS抬升超过阈值 V th,导致桥臂直通而烧毁。

b) 源极寄生电感引起的栅源电压振荡/失稳(SiC特有,危害极大)

根本原因:封装(如TO-247-4引脚电感)和PCB走线带来的源极寄生电感 Ls。

失效过程:

1. 器件开通时,漏极电流 I D急剧上升,其 di/dt 在VLS 上产生压降 VLs =+L S×di/dt。

2.这个压降使得源极引脚电位高于驱动地电位,导致实际加在芯片栅源两极的电压 V GS_intrinsic=V GS_pin −V Ls降低,可能使开通变慢甚至引起关断。

3.更危险的是关断和续流阶段。关断后,电流转移到续流二极管(体二极管或并联肖特基)。当对管开通,开关节点电压快速变化时,续流二极管的反向恢复dV/dt 会通过 CGD 耦合电流,并与L S形成LC谐振电路,引发栅极电压 VGS 的高频严重振荡。

4.振荡的 V GS峰值可能超过正向阈值导致误导通(直通),也可能跌破负压极限导致栅氧过压击穿。

c) 桥臂串扰

上管关断/下管开通时,开关节点电压的快速下降(高 -dV/dt)会通过下管的 C GD 耦合,抬升下管的栅极电压,可能导致下管提前导通形成直通。

2. 失效特征:

失效常与误导通/直通相关,D-S、G-S都可能短路。在失效前的波形上,可以观察到 V GS 在开关过程中存在剧烈的高频振荡。

3. 解决方案:

优化驱动回路以抑制源极电感影响:

首选开尔文源极(Kelvin Source)封装(如TO-247-4, D2PAK-7)。将驱动回流路径(Source Sense)与功率电流主路径(Power Source)分开,从根本上消除了功率电流 di/dt 对驱动电压的干扰。

若使用标准封装,必须将栅极驱动地线与功率源极引脚以最短、最宽、对称的方式直接连接,且单点接地。

增强驱动能力与稳定性:

采用双极性驱动电压(如+15V/-5V 或 +18V/-3V),提供强大的负压钳位。

选择具有强下拉(高拉电流)能力和有源米勒钳位(Active MillerClamp) 功能的专用SiC驱动IC。

在栅极串联电阻 R g 上并联一个反向肖特基二极管(从源极指向栅极),为关断时的米勒电流提供一条低阻抗的快速泄放路径,是抑制米勒导通非常有效且低成本的方法。

调整开关速度:在保证效率的前提下,适当增大栅极电阻 R g 以降低开关dV/dt,牺牲一点速度换取系统鲁棒性。通常需要平衡调整开通和关断电阻。

在桥臂中点增加RC缓冲电路:直接吸收开关节点的电压尖峰并减缓dV/dt,对抑制串扰和栅极振荡效果显著。

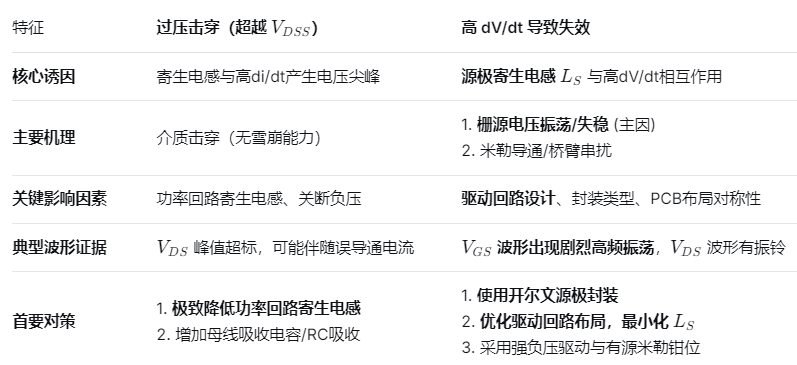

总结与对比(针对SiC MOSFET)

最终建议

把布局当作第一设计要务:对于SiC,糟糕的PCB布局几乎必然导致失效。必须遵循厂商的布局指南。

示波器诊断是金标准:必须使用高压差分探头和带宽足够(>200MHz)的示波器,同时测量:

芯片引脚处的 V DS(非母线远端)

芯片引脚处的 V GS(非驱动IC输出端)

漏极电流 I D观察三者之间的时序关系和振荡情况。

3.循序渐进:测试时,先从高栅极电阻、低母线电压、轻负载开始,逐步提高条件,并时刻监测波形是否出现振荡或电压尖峰超标。

4.善用数据手册:仔细阅读器件手册中关于驱动电压、最大电压、布局和吸收电路的所有警告和推荐。

总而言之,碳化硅MOSFET的失效更多地源于其“高速”特性引发的系统性问题(寄生参数、驱动回路),而非器件本身的极限能力不足。成功的应用取决于能否提供一个“安静、稳定、低感”的电磁环境和“果断、强劲”的驱动。

碳化硅MOSFETs与SiC功率模块产品概览

芯耀

芯耀

2309

2309