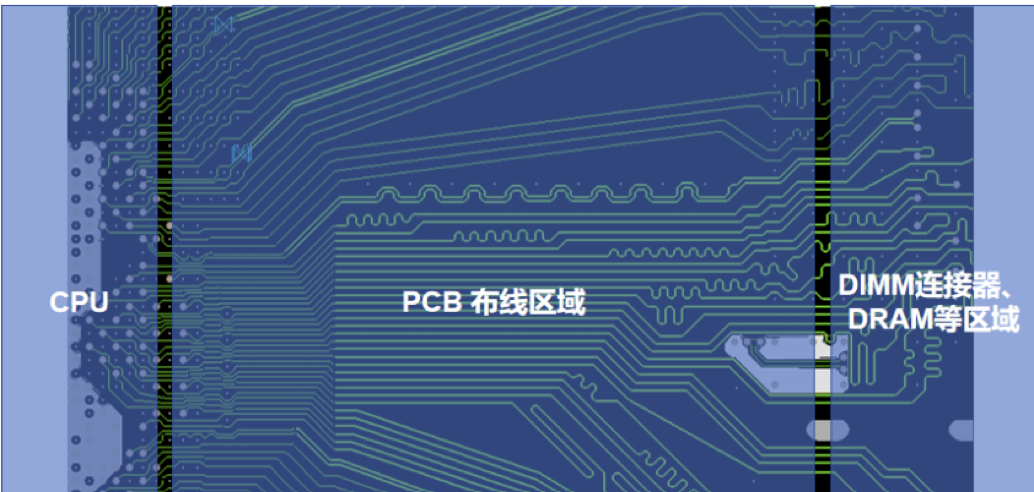

DDR PCB布线整体示意图,大体上可以分为三个部分:CPU区域,布线区域,以及DIMM连接器或DRAM区域。

对CPU区域和部分布线区域进行展开和细化,某设计图如下图所示。对于此PCB设计,假设传输线阻抗要求为40ohm,对应线宽为6mil,符合PDG要求的线间距为18mil。

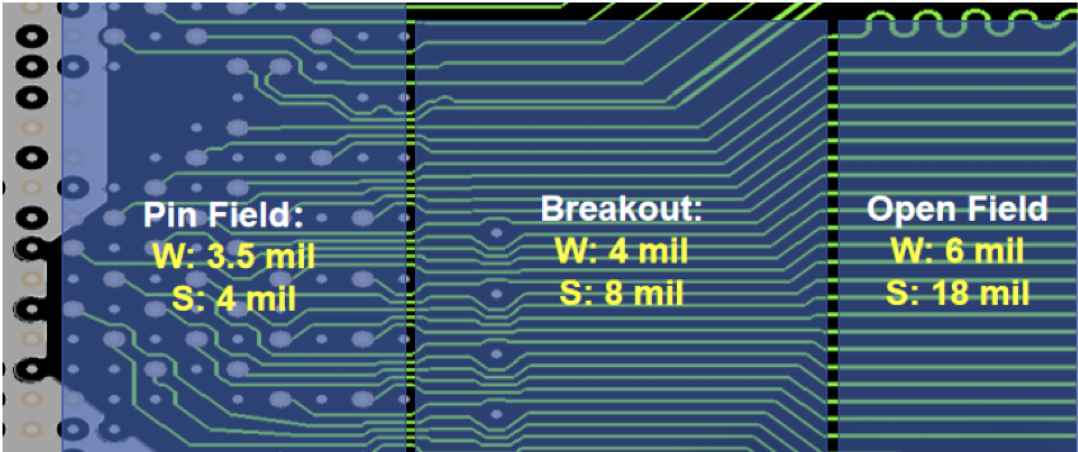

Pin Field指CPU/BGA区域BGA Ball和对应过孔的区域,这个区域的特点是PCB空间被BGA的Pad及引线出来的过孔大幅占据,所以传输线的布线面积相对就会变小,为了在有限区域可以把信号线走出去,必然要采用线宽较细、间距较小的方式完成信号出线。

下图为一个PCB表层布线示例,此处的传输线宽度只能是3.5mil,相对于6mil的正常线宽,阻抗必然会变大,造成整个信号链路的阻抗不连续。同时,线间距会不均匀且小于正常布线间距,比如4mil,那么相对于18mil正常的线间距,串扰也会增加。

Pin Field还有一种形式,对于内层Stripline,对于多通道DDR布线,BGA区域走线深度会比较深,只能从各个Via之间穿过,而一般2个Via之间只能穿过宽度大约为3.5mil,间距为4mil的一对走线,其阻抗也会变大。如果是较为理想的Stripline,我们暂且认为且远端串扰比较小。

Pin Field之后的一段线,被称为Breakout,其特点是具有完整的布线空间,但因为DDR信号线密集,需要一段区域将其扇开,所以Breakout区域空间也相对有限,一般采用线宽为4mil、间距为8mil的方式进行走线,相对于正常的6mil线宽、18mil间距走线,其阻抗和串扰也会较大。

经过Breakout区域扇出之后,就有整片区域(Open Field)可以按照设计规则,进行正常布线。

对于DDR设计,信号反射和串扰是两个主要问题,所以,工程师和设计人员在进行布线时,需要尽可能使阻抗一致或接近,串扰尽可能小。

常规的方式是要尽可能采用正常线宽间距进行布线,同时尽量减小Pin Field和Breakout区域的走线长度,但设计难度会更高,且整体成本会大幅上升,因为需要更多的走线层来完成BGA区域的出线。

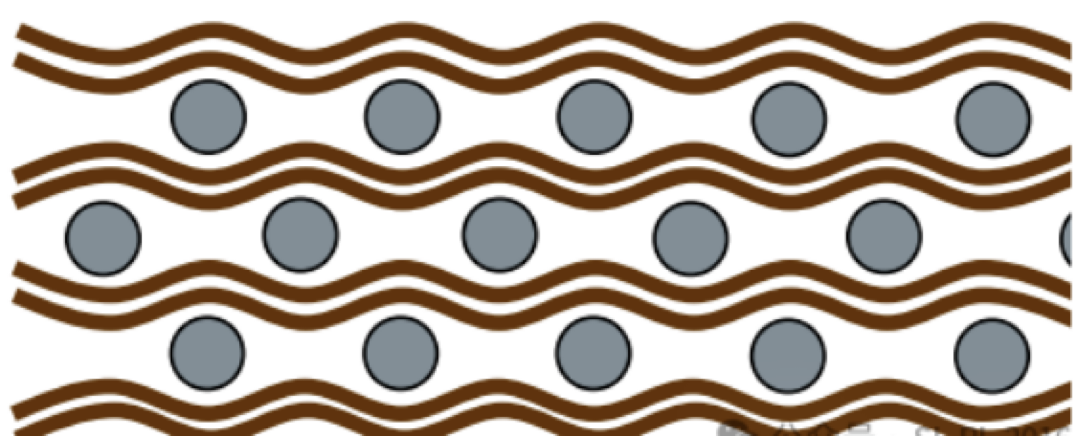

所以,在Pin Field和Breakout区域布线长度无法减小的情况下,Intel提出了Tabbed Routing的布线方式,通过在这些区域,增加一些Tab,来补偿阻抗一致性,以及减小远端串扰。

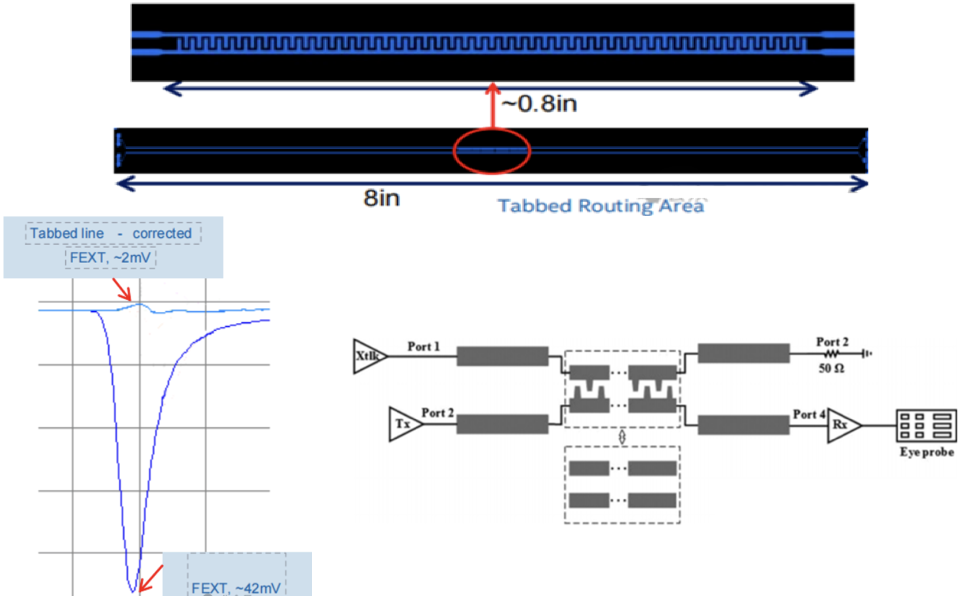

增加Tab,就是变相增加线宽,所以其阻抗会变小。对于一对Microstrip Line, 其耦合长度为8 inch(此示例来自Intel公开文档),通过仿真结果可以看出,对比有和没有Tabbed Routing的远端串扰值,从之前的42mV减小到了2mV。当然,在实际应用中,由于PCB区域的限制,不能随意改变Tab的尺寸,效果可能会有不同差异。

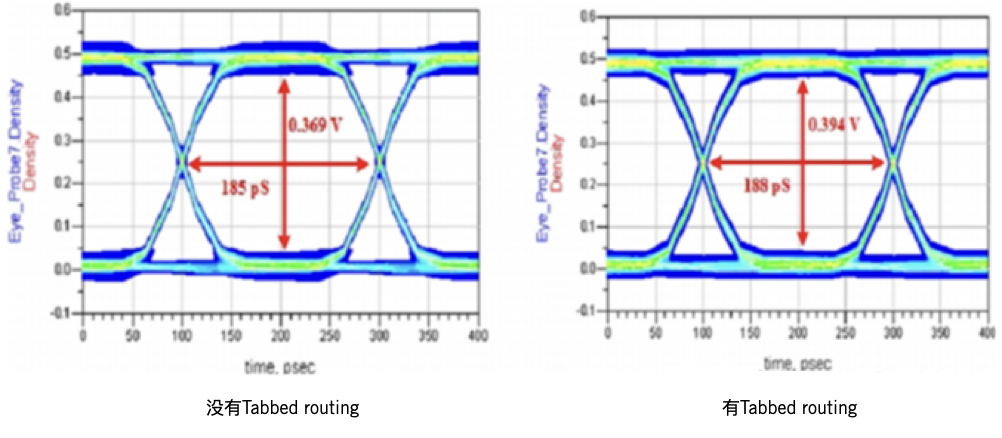

对比其传输线有没有使用Tabbed routing的效果,眼图仿真结果如下,可以看到加了Tabbed routing以后,眼宽和眼高均有不同程度的改善。

Tabbed Routing设计和应用

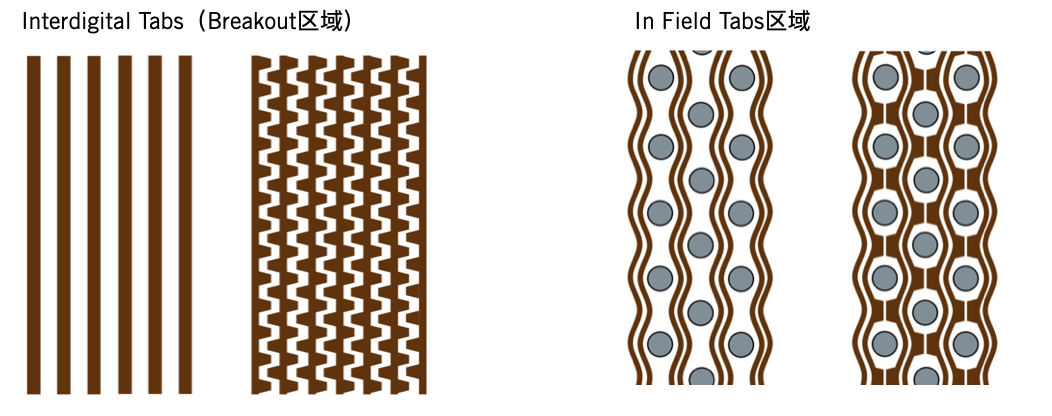

在PCB设计中,Tabbed routing通过在不同区域使用不同类型的Tab来优化信号完整性和阻抗匹配,以下是几种常见Tab的区别。

具体的项目设计中,根据不同PCB形状和布线区域,可以有各种不同的设计方法:

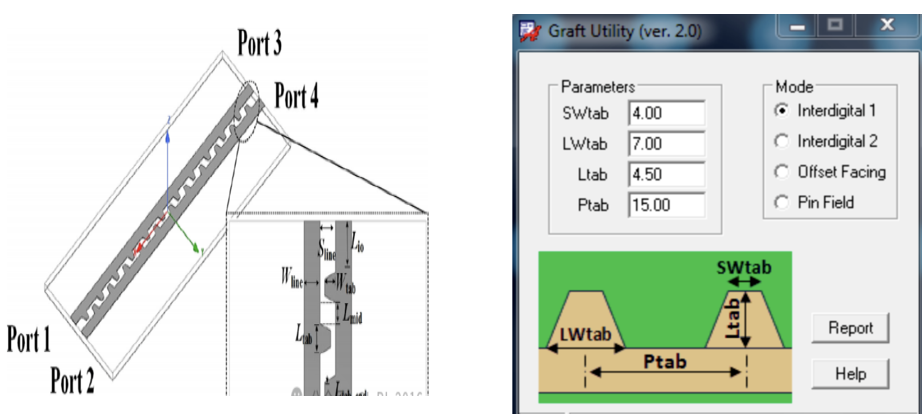

Tabbed Routing的结构,一般用几个参数来确定。项目设计中,Allegro等主流设计工具中,已经集成了Tabbed Routing的设计插件,只要输出各个参数,就可以自动完成设计。

总的来说,Facing Tabs在Pin Field和Open Field区域都有应用,侧重于控制互容和阻抗以优化信号完整性;Pin Field Tabs专门用于Pin Field区域的阻抗匹配;Interdigital Tabs则主要在外层开放区域解决走线密集和串扰问题。

Tabbed Routing是否适用于颗粒DDR

使用Tabbed Routing进行布线时,还需注意Tab会增加信号间的耦合,若靠近其它信号线,额外铜箔会增加电容耦合或电感耦合,导致串扰增加。不当设计的Tab还可能在特定频率产生谐振,放大高频噪声,加剧串扰。

同时,需要通过仿真优化Tab的尺寸、间距等参数,设计过程较为复杂,增加Tab会增加PCB制造难度,提高制造成本和生产周期。

总结

Tabbed Routing是Intel发明的一种针对布线空间不足的创新设计方式,可以在有限空间内,进行阻抗补偿和远端串扰的改善,从而改善整个链路的信号性能。这种布线方式,广泛应用于DDR的PCB设计中,也可以应用在封装、Interposer等领域。对于一些布线空间充足、信号速率不高、对信号完整性要求较低的电路,并不需要采用这种方式,因为其带来的收益可能无法弥补设计和制造成本的增加。

参考资料

芯耀

芯耀

2786

2786