为确保碳化硅(SiC)功率器件在过载 、短路等工况下能安全可靠地工作 ,必须充分认识 SiC 器件的短路机理 。 首先对 SiC MOSFET 硬开关短路故障下短路电流原理进行了分析 ,在此基础上对不同电路参数对 SiCMOSFET 短路特性的影响进行了对比分析 ,揭示了短路特性的关键影响因素 ,并对 Si 与 SiC MOSFET 短路能力和器件恶化机理进行了对比分析 ,从而为设计 SiC MOSFET 短路保护电路提供一定的指导 。

与硅(Si)功率器件相比 ,碳化硅(Silicon car-bide ,SiC)功率器件具有更优电气特性和热特性[1] ,可大幅提高电力电子变换器的性能 ,在工业[2-4] 、高温高频[5-9]和可再生能源发电[10 ]等诸多场合中已获得初步应用 。 随着 SiC 工艺技术的日趋成熟 ,SiC 功率器件有望取代传统的 Si 功率器件 ,在未来的电力电子变换器中获得更为广泛的应用与发展 。 目前 ,SiC MOSFET 是商业化程度最高的 SiC 可控功率器件 。 但是 ,由于 SiC MOSFET 管芯面积小 ,电流密度大[11] 且短路能力较弱 ,因此对电路保护要求更高 ,给 SiC 基电力电子变换器的可靠性带来极大挑战 ,特别是在大功率场合 ,这一问题更加突出 。 因此 ,SiC MOSFET 短路特性及其稳健性逐渐受到研究人员的关注 ,成为SiC MOSFET 重要研究内容之一 。

近些年 ,国内外诸多学者针对 SiC 功率器件的短路特性进行了研究 。 文献[12]对 SiC MOSFET的短路稳健性进行了研究 ,得出 400 V 直流母线电压下 SiC MOSFET 短路承受时间约为 30 μs 。 文献[13]在 600 V 直流母线电压下分别对相同电压定额的两种 SiC MOSFET 的短路稳健性进行了研究 ,得出两者的短路承受时间分别为 5 μs 和14 μs 。 文献[14]对不同直流母线电压下 Si 和 SiCMOSFET 的短路特性进行了对比和研究 。 但是 ,这些研究只针对不同直流母线电压的 SiC MOSFET 短路特性进行了研究 ,忽略了驱动回路参数的影响 。 另外 ,这些研究大多只是对实验现象的定性描述 ,缺乏进一步深入分析 。 因此 ,本文首先对SiC MOSFET 短路机理进行了分析 ,在此基础上对不同电路参数对其短路特性的影响进行了对比和研究 ,揭示了短路特性的关键影响因素 ,并对器件短路能力及恶化机理进行了对比分析 ,为研究人员设计 SiC MOSFET 短路保护提供了一定的指导 。

1、短路故障类型及测试电路

功率器件的短路故障类型可分为硬开关故障(Hard switching fault , HSF )和负载故障 (Faultunder load ,FUL ) 。 硬开关故障是指在开关管开通时发生短路故障 ,即在开关管开通之前 ,负载已经短路 ,电源电压直接加在开关管两端 。 当开关管开通时 ,就会在电路中形成一个低阻抗回路 ,导致流过开关管的电流急剧上升 。 而负载故障是指在开关管完全导通时发生短路故障 ,即在发生短路故障之前 ,开关管导通 ,电路处于正常工作状态 。 当负载突然短路时 ,就会在电路中形成一个低阻抗回路 ,导致回路电流急剧上升 。 由于硬开关故障下 ,SiC MOSFET 功率损耗更大 ,发热更严重 ,对器件的考验更为严峻 ,所以本文对 SiC MOSFET 的硬开关故障进行了原理分析 。

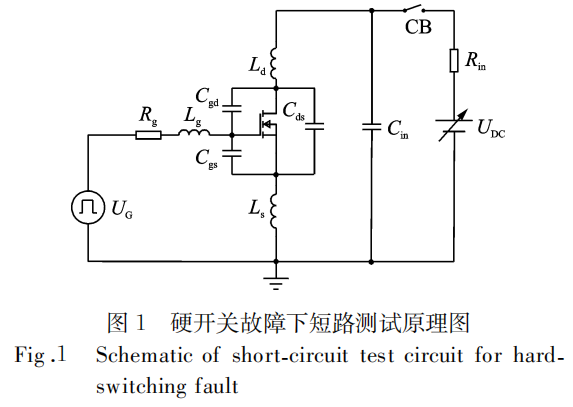

图1 为硬开关故障模式下 SiC MOSFET 短路特性测试原理图 。 UDC为可调直流电源 ,Rin为电源内阻 ,CB 为断路器 ,UG 为单脉冲驱动信号 ,Rg 为驱动电阻 ,Cgs ,Cgd 和 Cds 为 SiC MOSFET 的寄生电容 ,Lg ,Ld 和 Ls 分别为包括器件外部引线和器件内部连线的栅极 、漏极和源极的寄生电感 。

2、SiC MOSFET 短路原理分析

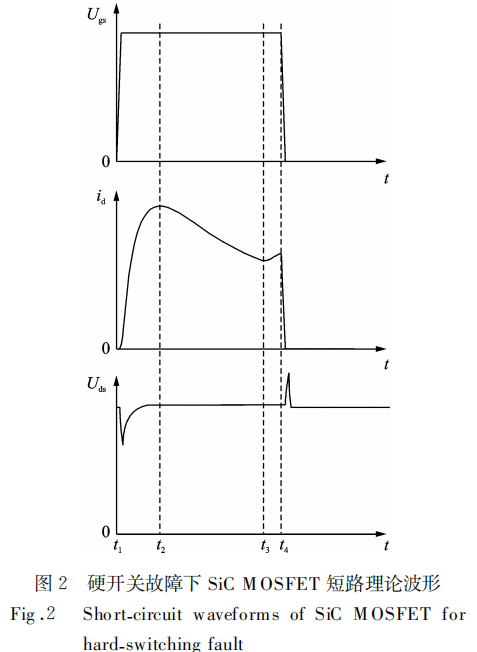

硬开关故障下 SiC MOSFET 短路原理波形如图 2 所示 ,可以分为 4 个工作模态 。

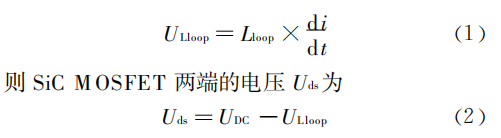

模态 1[t1 ~ t2 ] :t1 时刻之前 ,SiC MOSFET 处于截止状态 。 此时 ,断路器 CB 闭合 ,直流母线电压 UDC直接加在 SiC MOSFET 两端 。 t1 时刻 ,SiCMOSFET 开通 。 由于功率回路阻抗很小 ,SiCMOSFET 漏极电流急剧增大 。 同时 ,短路电流变化率 di/dt 作用于回路寄生电感 Lloop (Lloop = Ld +Ls ) ,在 Lloop上产生一个与直流母线电压极性相反的电压 ULloop ,导致 SiC MOSFET 漏源极电压有所下降 。 ULloop可表示为

在短路电流上升过程中 ,SiC MOSFET 的功率损耗导致自发热 ,SiC MOSFET 结温逐渐升高 ,导通电阻也随之逐渐增大 ,导致 d i/d t 逐渐减小 ,这是因为在短路回路中 SiC M OSFET 导通之后 ,导通电阻 、寄生电感组成了一个一阶 LR 串联电路 ,随着导通电阻的增大 ,回路阻抗增大 ,电流上升速率有所降低 ,SiC MOSFET 漏源极 Uds又逐渐升高 。 t1 ~ t2 阶段内 ,SiC MOSFET 沟道载流子迁移率具有正温度系数 ,故短路电流一直增大 。 但 SiCMOSFET 自身功率损耗很大 ,导致自发热 ,开关管结温快速升高 。

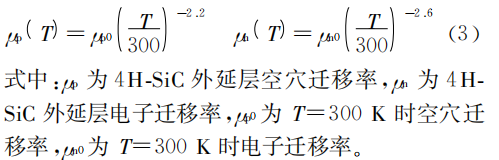

模态 2[t2 ~ t3 ] :随着 SiC MOSFET 结温的升高 ,t2 时刻 SiC MOSFET 沟道载流子迁移率开始降低 ,导致流过开关管的电流减小 ,di/dt 为负 。在这一阶段 ,SiC MOSFET 沟道载流子迁移率具有负温度系数 ,可表示为

模态 3[t3 ~ t4 ] :随着结温的进一步升高 ,t3 时刻 ,SiC MOSFET 沟道载流子电流减小的速率小于热电离激发漏电流增大的速率 ,短路电流又逐渐变大 ,di/dt 为正 。

模态 4[t4 ~ ] :t4 时刻开关管关断 ,开关管端电压出现关断过压 ,电流逐渐减小到零 ,此后会出现两种情况 :(a)开关管安全可靠关断 ;(b)开关管栅极氧化层击穿 ,器件失控 。

3、电路参数对短路特性的影响

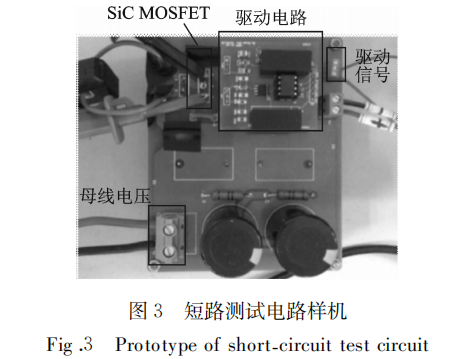

影响 SiC MOSFET 短路特性的因素包括栅极驱动电路参数和直流母线电压 。 为了量化分析各电路参数对 SiC MOSFET 短路特性的影响 ,制作了短路测试平台 ,如图 3 所示 。 待测 SiC MOSFET 采用 ROHM 公司的 SCH2080KE ,其定额为1 200 V/35 A 。 测试中直流电源采用 Chroma 公司 62150H-600 型可编程稳压直流电源 。 功率器件的电压和电流波形通过 Tektronix 公司的高压差分探头(P5201 ) 、高频电流探头(TCP303 )和电流探头放大器 (TCPA300 )测得 。 实验测试条件为 :寄生电感 L = 0 .18 μH ,SiC MOSFET 驱动电路负向驱动电压设定为 - 2 V 。

3 .1 直流母线电压的影响

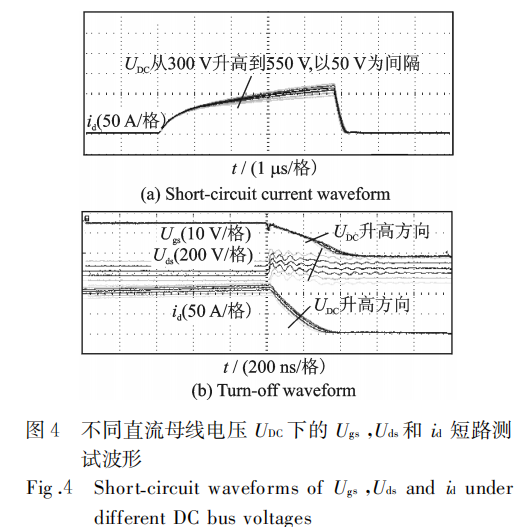

图 4 给出不同直流母线电压 UDC 下 ,栅源极电压 Ugs ,漏源极电压 Uds 和漏极电流 id 的短路测试波形 。 直流母线电压升高 ,短路电流上升速度更快 ,短路峰值电流也逐渐增大 ,同时栅源极电压Ugs下降时间变长 ,关断过压变化幅度较小 。 测试中短路脉宽设定为 5 μs ,此时 SiC MOSFET 管芯内部结温并不高 ,沟道载流子迁移率具有正温度系数 ,di/dt 为正 ,短路电流一直增大 。

3 .2 驱动电阻的影响

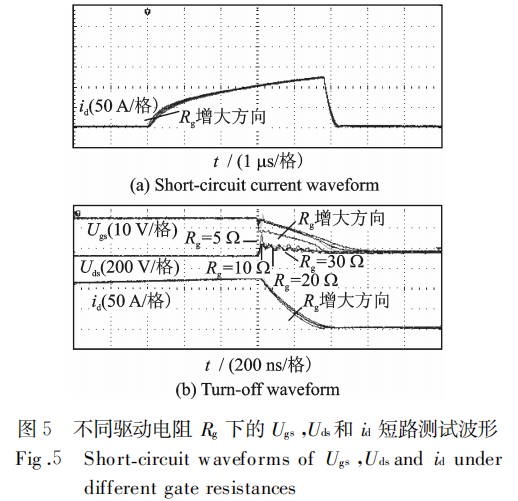

直流母线电压为 550 V ,驱动电阻 Rg 分别取30 ,20 ,10 和 5 Ω 。 图 5 给出不同驱动电阻下 ,栅源极电压 Ugs ,漏源极电压 Uds 和漏极电流 id 的短路测试波形 。 随着驱动电阻的减小 ,SiC MOSFET关断速度更快 ,漏源极电压和栅源极电压的振荡略有增大 ,而短路电流波形几乎没有变化 ,不同驱动电阻下的短路峰值电流保持不变 ,这是因为驱动电阻主要影响短路电流初期的上升速度 ,驱动电阻减小会加快短路电流初期的上升速度 ,但对短路电流波形和短路峰值电流几乎没有影响 。

3 .3 栅极驱动电压的影响

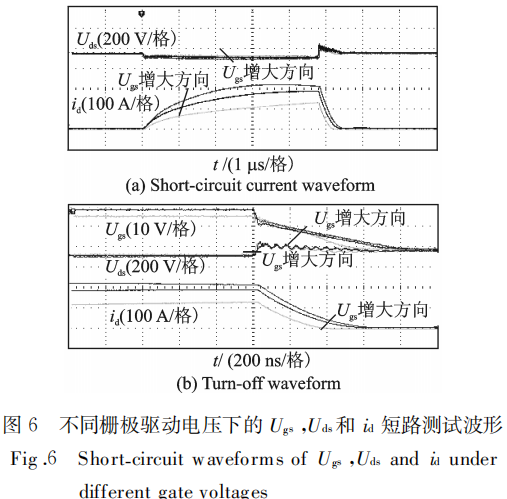

直流母线电压为 550 V ,驱动电阻为 30 Ω ,由于 SCH2080KE 型 SiC MOSFET 栅极正向电压极限值为 + 22 V ,考虑一定的安全裕量 ,驱动电压分别取 + 20 ,+ 18 和 + 15 V 。 图 6 给出不同栅极驱动电压下 ,栅源极电压 Ugs ,漏源极电压 Uds和漏极电流 id 的短路测试波形 。 由图 6 可见 ,栅极驱动电压对 SiC MOSFET 短路电流影响比较明显 。SiC MOSFET 开通瞬间 ,随着栅极驱动电压的升高 ,短路电流上升速度越快 ,短路峰值电流越大 。当栅极驱动电压为 + 20V 时 ,短路电流达到峰值后开始逐渐减小 ,即 di/dt 开始为负 ,这是由于短路峰值增大导致功率管损耗大大增加 ,SiC MOSFET内部结温进一步升高使沟道载流子迁移率降低 。

3 .4 电路参数影响的量化分析

为了进一步明确电路参数对短路特性的影响程度 ,对各电路参数与关断过压 、短路峰值电流及短路能量的影响进行了量化分析 。

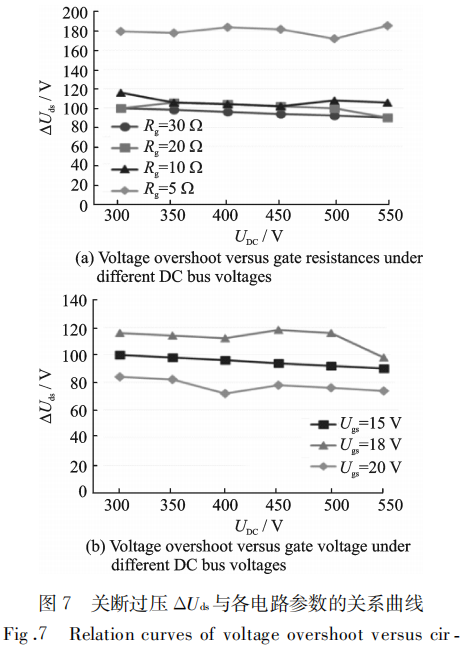

(1)对关断过压的影响

图 7 给出关断过压 ΔUds与各电路参数的关系曲线 。 直流母线电压升高 ,关断过压变化幅度较小 ,约为 20 V 。 驱动电阻越小 ,关断速度越快 ,d i/压d t越 在 大 回路,且 寄 驱 生 动 电 电 感 阻 上R产g 为 生的5电Ω压 时 越,关 高 断,过 即关 压 断 约 过 是Rg 为 30 Ω 时关断过压的 2 倍 。 栅极驱动电压越高(低于 20 V) ,短路电流越大 ,关断过压越大 。 由于栅极驱动电压的增大 ,SiC MOSFET 沟道电阻减小 ,导致了短路电流峰值的增大 。 关断过压的增大是由于关断过程中 di/dt 的增大 ,与回路中寄生电感相互作用引起的感应电压增大 。 当栅极驱动电压达到 20 V 时 ,关断过压减小 ,这是由于短路损耗增大 ,器件结温大大升高 ,SiC MOSFET 沟道载流子迁移率减低 ,导致短路电流减小 。 同时 ,由于此时器件内部结温较高 ,SiC MOSFET 开启电压降低 ,关断速度降低 ,所以过压减小 。

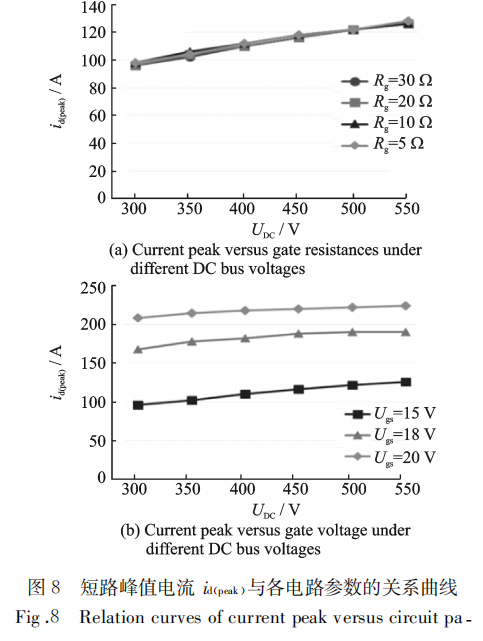

(2)对短路峰值电流的影响

图 8 给出短路峰值电流 id(peak)与各电路参数的关系曲线 。 短路峰值电流与直流母线电压正相关 ,驱动电阻对短路峰值电流几乎没有影响 ,但栅极驱动电压对短路峰值电流影响较大且电压越高 ,峰值电流越大 ,栅极驱动电压 Ugs 为 20 V 时 ,短路峰值电流约为 Ugs为 15 V 时的 2 倍 。 此外 ,当栅极驱动电压较低时(如 15 V) ,短路峰值电流与直流母线电压近似为线性关系 ,变化幅度较大 。 而当栅极驱动电压较高时(如 20 V) ,随着直流母线电压升高 ,短路峰值电流增长幅度趋于平缓 。

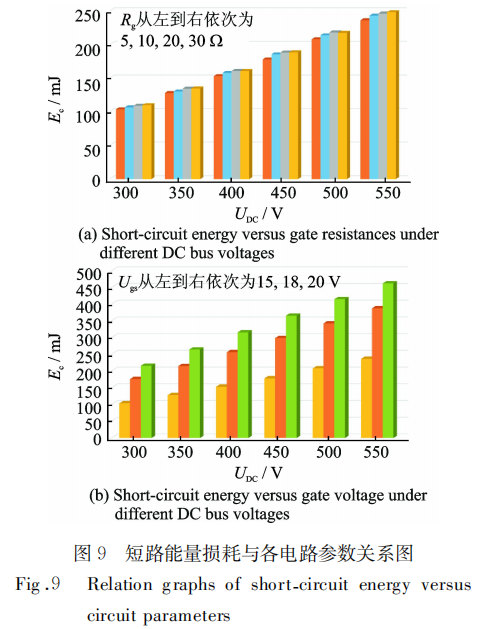

(3)对短路能量的影响

图 9 给出了短路能量 Ec 与各电路参数的关系图 。 显然 ,随着母线电压的升高 ,短路能量不断增大 。 而驱动电阻减小 ,短路能量略有增大 。 另外 ,由前述分析可知 ,栅极驱动电压对关断过压 、短路峰值电流有很大的影响 ,故短路能量对栅极驱动电压较为敏感 。 栅极驱动电压 Ugs 为 20 V 时 ,短路能量是 Ugs为 15 V 时的 2 倍左右 。

由以上分析比较可知 ,栅极驱动电阻 Rg 对关断过压影响较大 ,而对短路峰值电流几乎没有影响 ;直流母线电压对短路峰值电流的影响较大 ,栅极驱动电压 Ugs 对关断过压和短路峰值电流的影响均较大 。 在设计短路保护电路时 ,往往采用“软关断”技术 ,即增大关断时的驱动电阻以降低开关管的关断速度 ,达到降低开关管电压应力的目的 ,但该方法并不能降低开关管的电流应力 。 另外 ,相比于栅极驱动电阻 Rg ,栅极驱动电压 Ugs对关断过压和短路峰值电流的影响更为显著 ,若设计保护电路时采用“多电平关断” ,既可以有效降低开关管的电压应力 ,又能大大减小开关管的短路电流应力 ,确保开关管可靠关断 ,但该方法增大了保护电路设计的复杂性 。

4、短路能力及器件恶化分析

4 .1 短路能力

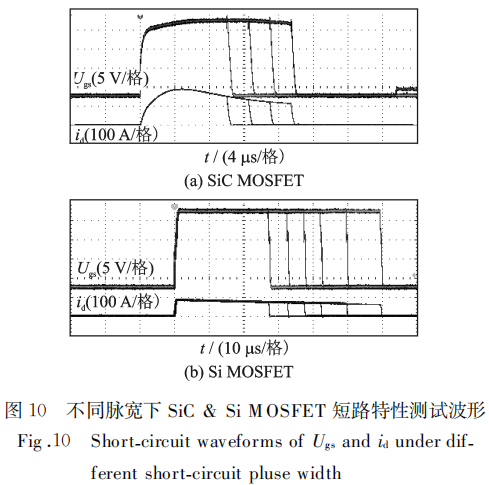

为 探 究 MOSFET 的 短 路 能 力 ,分 别 对1 200 V SiC MOSFET (SCH2080KE)和 Si MOSFET (IXFH12N120P)在不同脉宽下的短路特性进行了测试 ,测试波形如图 10 所示 。

短路脉宽初始值设置为 10 μs ,可以看出 ,短路电流先增大后减小 ,与前述分析一致 。 随着短路脉宽的进一步增大 ,关断时短路电流逐渐减小 ,但短路能量逐渐增大 。 当短路脉宽增大至 15 μs 时 ,SiC MOSFET 通态时的栅源极电压 Ugs 已略有下降 ,说明此时栅极漏电流增大 ,器件性能开始恶化 ;当短路脉宽进一步增大至 17 .5 μs 时 ,其通态时的栅源极电压 Ugs下降幅度已增大至 2 V ,同时在 SiCMOSFET 关断后 ,经 12 μs 延时 ,栅源极电压 Ugs变为 0 V ,SiC MOSFET 栅源极已经短路 ,器件损坏 ,此时应对的短路能量 Ec 为 1 .365 J 。 而与之对应的 Si MOSFET ,在短路脉宽为 17 .5 μs 时 ,器件依然保持良好的性能 ,即使脉宽增大至 60 μs(短路能量 Ec 为 2 .403 J)仍能有效地断开短路电流 ,同时栅源极未被击穿 。

4 .2 器件恶化分析

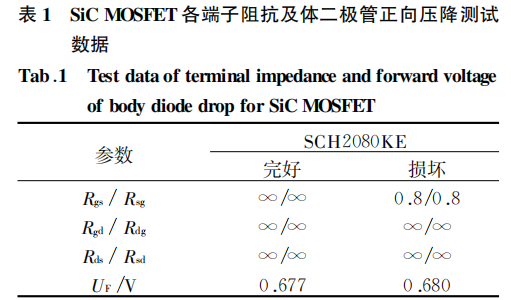

表 1 给出正常和损坏的 SiC MOSFET 各端子阻抗及体二极管正向压降测试数据 。 可见 ,母线电压为 550 V ,短路脉宽为 17 .5 μs 时 ,SiC MOSFET栅源极氧化层被击穿 ,栅源极近似短路 ,此时 SiCMOSFET 为不可控器件 ,但是其漏源极阻抗依然很大 ,具有一定的阻断能力 ,同时体二极管正向压降几乎保持不变 。

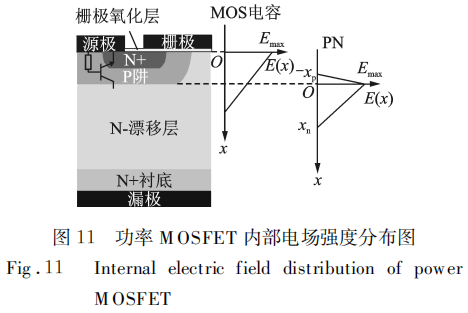

短路时 ,直流母线电压 UDC 直接加在 MOSFET 两端 ,由于 MOSFET 栅源极电压一般只有十几伏 ,故直流母线电压由反向偏置的 PN 结(漏源极寄生电容 Cds )和 MOS 电容(栅漏极寄生电容Cgd )共同承担 ,图 11 给出功率 MOSFET 内部电场强度分布图 。

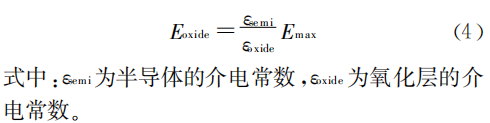

由高斯定理可知 ,栅极氧化层中电场强度与其下方半导体材料电场强度满足

对于 SiC/SiO2 (或 Si/SiO2 ) ,εsemi /εoxide ≈ 2 .5 ,这意味着氧化层中电场强度是半导体中最大电场强度的 2 .5 倍 。 SiO2 的击穿场强为 10 MV/cm ,为保证氧化层的长期稳定性 ,氧化层中电场强度一般应小于 4 MV/cm 。 对于 Si MOSFET ,由于 Si的临界场强为 0 .3 MV/cm ,因此氧化层中的电场强度最大为 0 .75 MV/cm ,远小于 4 MV/cm 。 但对于 SiC MOSFET ,由于 SiC 的临界场强更高 ,其内部最大电场强度可达 Si MOSFET 的十几倍 ,使氧化层中电场强度很容易超过 4 MV/cm ,不利于氧化层的长期稳定 。 同时 ,为获得期望的阈值电压 ,SiC MOSFET 栅极氧化层厚度设计得更薄 ,势垒宽度更窄 ,根据 Fowler-Nordheim 沟道理论 ,当栅源极施加正向偏置电压时 ,反型层表面的电子会进入或穿过氧化层 ,进而产生沟道电流 ,即栅极漏电流 。 短路时 ,器件内部结温迅速升高使栅极漏电流大大增大 。 当该漏电流达到一定值就会导致氧化层电介质击穿 ,产生界面缺陷 ,最终导致器件恶化 。

5、结 论

本文对 SiC MOSFET 的短路特性进行了研究 ,将不同电路参数对短路特性的影响进行了对比分析 ,并对功率 MOSFET 短路能力及器件恶化机理进行了研究 ,得出以下结论 :(1)栅极驱动电阻Rg 对短路峰值电流和短路能量影响很小 ,而对关断过压影响较大 。 (2)直流母线电压对短路峰值电流和短路能量变化影响较大 ,而关断过压变化影响较小 ,约为 20 V 。 (3)栅极驱动电压对 SiC MOSFET 短路特性的影响最为显著 。 栅极驱动电压Ug s由 15 V 增大至 20 V ,SiC MOSFET 短路峰值电流和短路能量约增大了两倍 。 设计短路保护电路时 ,为关断 SiC MOSFET 可适当降低栅极电平 ,这有益于 SiC MOSFET 安全关断 ,提高电路的可靠性 。 (4)由于 SiC MOSFET 阈值电压的要求及SiC 材料的特殊性 ,SiC MOSFET 的栅极稳定性更差 ,短路能力更弱 。 虽然随着工艺的进步 ,SiCMOSFET 栅极氧化层稳定性有所提高 ,但快速有效的保护无疑是确保 SiC MOSFET 安全工作的最佳办法 。

了解更多三代半碳化硅MOS与SiC模块信息,请关注微信公众号

芯耀

芯耀

2332

2332