名称:音频采集与延时回放系统设计Verilog代码VIVADO仿真

软件:VIVADO

语言:Verilog

代码功能:

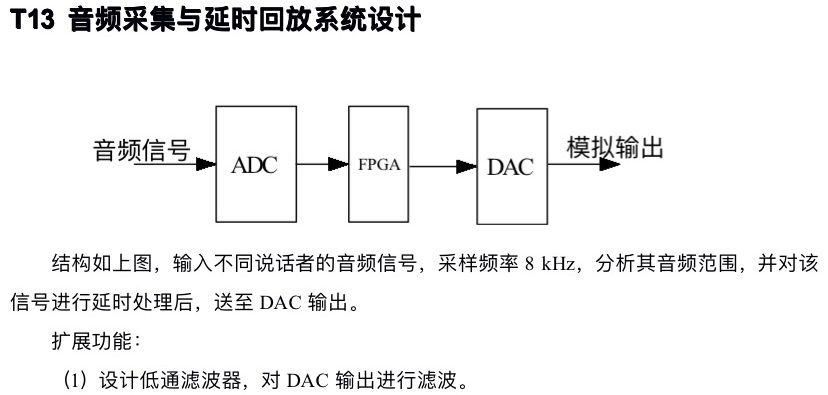

输入不同说话者的音频信号,采样频率8kHz,分析其音频范围,并对该信号进行延时处理后,送至DAC输出

扩展功能:

(1)设计低通滤波器,对DAC输出进行滤波。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

演示视频:

设计文档:

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. Testbench

6. 仿真图

整体仿真图

AD控制模块

延迟模块

DA控制模块

部分代码展示:

//AD9226控制模块 module AD_ctrl( input clk,//时钟50MHZ input rst_p,//复位 input [11:0] AD_DB,//12位AD采样值 output AD_clk,//输出AD采样时钟 output reg [11:0] AD_data//AD采样值 ); //50MHz分频到8KHz,需要计数6250 reg [15:0] div_cnt; always@(posedge clk or posedge rst_p) if(rst_p) div_cnt<=16'd0;//复位 else if(div_cnt<16'd6250) div_cnt<=div_cnt+16'd1;//计数 else div_cnt<=16'd0;//清零,循环计数0~6249 //8K信号 reg clk_8K; always@(posedge clk or posedge rst_p) if(rst_p) clk_8K<=0; else if(div_cnt>16'd3125)//6250的一半,一半为高电平,一半为低电平 clk_8K<=1;//8K信号,高电平 else clk_8K<=0;//8K信号,低电平 assign AD_clk=clk_8K;//输出AD采样时钟

点击链接获取代码文件:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=1011

阅读全文

芯耀

芯耀

814

814