在电子电路设计中,共模抑制比(Common Mode Rejection Ratio,CMRR)是一个关键参数,常用于描述电路对于共模信号的抑制能力。特别在运放(Operational Amplifier,Op-Amp)应用中,共模抑制比影响着电路的性能稳定性和准确性。本文将探讨共模抑制比的定义、计算方法以及在运放应用中的重要性。

1. 共模抑制比的定义与计算

1.1 概念

1.2 计算方法

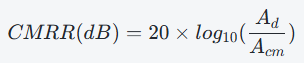

- 共模抑制比通常使用对数形式表示,单位为分贝(dB)。计算公式如下:

其中,Ad 是差模增益,Acm 是共模增益。

2. 共模抑制比在运放中的重要性

2.1 提高信号精度

- 在运放应用中,共模抑制比直接影响着信号处理的精度。高CMRR意味着运放能够更好地区分差分信号和共模干扰,从而提高信号处理的准确性。

2.2 抑制噪声

2.3 改善系统稳定性

- 系统的共模抑制比决定了其对外部环境变化的适应能力。一旦系统受到共模干扰,可能导致系统不稳定,因此高CMRR可以帮助提高系统的稳定性。

2.4 增强信号传输可靠性

3. 高共模抑制比的实现方式

3.1 差分输入

- 采用差分输入结构可以有效增加共模抑制比,减小共模干扰的影响。

3.2 良好的布局设计

- 合理的布局设计可以减小共模干扰的产生,提高整个系统的共模抑制比。

3.3 选择高性能运放

- 选用具有较高共模抑制比的优质运放器件,是提高整体电路性能的有效途径。

阅读全文

芯耀

芯耀

659

659