数字化转型、AI和各行各业的上云需求,都在推动数据中心领域的蓬勃创新和发展。IDC数据显示,2021年上半年,中国大数据平台的整体市场规模达到54.2亿元,同比增长43.5%。海量的数据推动下,数据中心对更高速率网络协议的需求在升级,这些协议的速率大约每两年翻一倍,这给服务器和网络设备中的PCIe互联带来瓶颈。

着眼未来的数据密集型应用,PCIe 6.0规范在2022年1月正式发布,专为满足人工智能/机器学习、高性能计算、云计算和网络等众多数据中心领域日益增长的性能需求。作为在CPU、GPU、FPGA和特定工作负载加速器等各种计算节点之间传输数据的重要骨干,PCIe 6.0的发布对下一代数据中心的建设具有哪些重要意义?又亟待需要哪些创新产品来推进落地?日前,Rambus在推出最新的PCIe 6.0控制器时,接受了媒体采访。

高速数据传输需求下的接口升级趋势

Rambus战略营销副总裁Matt Jones表示,为了支持庞大数据量的传输和存储,数据中心既要有完善的基础设施架构,也需要新的计算模式,如分解式计算(Disaggregated Computing)或者可组合式计算(Composable Computing),这对数据传输速率的提升和数据传输的安全性提出了更高要求。

Rambus战略营销副总裁Matt Jones

他指出,计算资源和计算模型正变得更加同构化或分散化,通用CPU和AI加速器常常被结合使用,并要求数据能够高速、安全地传递,这是PCIe标准向更高数据传输速率发展的核心需求。

应对这一趋势,业界必须尽可能更快、且更安全地在更远的距离上移动数据,例如CPU和AI加速器之间存在距离,但需要非常迅速的、安全的交换数据——这就是根本性的变化。

从PCIe标准的演进趋势来看,从PCIe 2.0到3.0/4.0,分别花费了5年和7年的时间,但从PCIe 4.0到5.0,再到6.0,时间间隔却分别只有2年和3年,并且,PCIe 6.0 64GT/s的传输速度是3.0标准的8倍。

PCIe性能加速曲线

PCIe 6.0有哪些新特性?

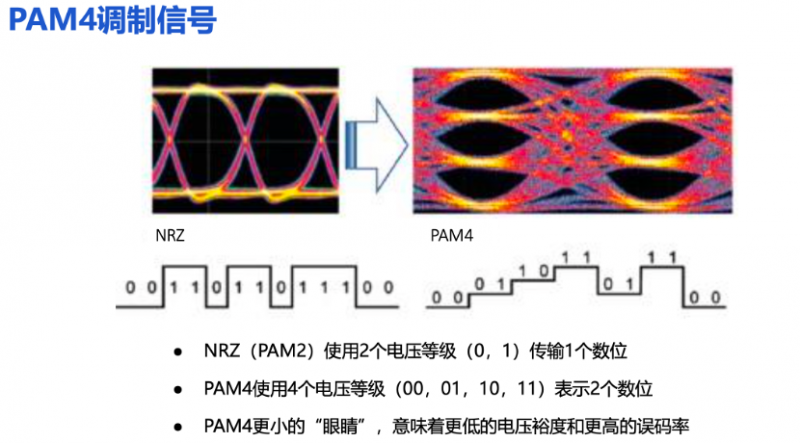

作为全新一代规范,PCIe 6.0的数据速率从32GT/s翻倍至64GT/s,为此,它主要增加了PAM4调制信号、前向纠错(FEC)、FLIT模式等功能创新。

具体而言,通过PAM4,每个时钟周期的数据传输可以达到2bit,而并不仅仅是单bit的数据传输。PAM4采用四个不同的电平等级,可在每个时钟周期表达2个数位,即从00、01、10再到11。这就意味着,在同样的电压波动范围内和同样的时钟周期内,由于PAM4的电压等级比PAM2高了两个,即眼图中黑色的区域“眼睛“部分更多、更小了,从而带来了更低的电压裕度和更高的误码率,使得在设备中保证信号完整性成为了一个非常关键的问题。

由于PAM4是确保PCIe 6.0达到64GT/s数据传输速率的关键,为此,PCIe 6.0采用了前向纠错技术(FEC)。FEC本质上是一种算法技术,可以在数据传输链路中确保所有信号的完整性。同时,FEC技术的采纳还改变了数据流控制单元的情况,要求开发人员也必须针对数据包本身的大小做出调整和改变。

为了更好地保证FEC技术的实现和操作,PCIe 6.0没有采用前几代规范可变大小的数据包,而是固定大小数据包(FLIT),以更好地保证FEC技术的实现和操作。

此外,考虑到数据传输速率的上升和PAM4技术本身会增加设备的功耗,每一比特数据传输造成的单位数据能耗也会增加。为了减少整体系统的能耗,PCIe 6.0采用了L0p模式,通过动态的信道分配,允许将每个通道进行封闭或者打开来实现系统性的节能。

全新PCIe 6.0控制器

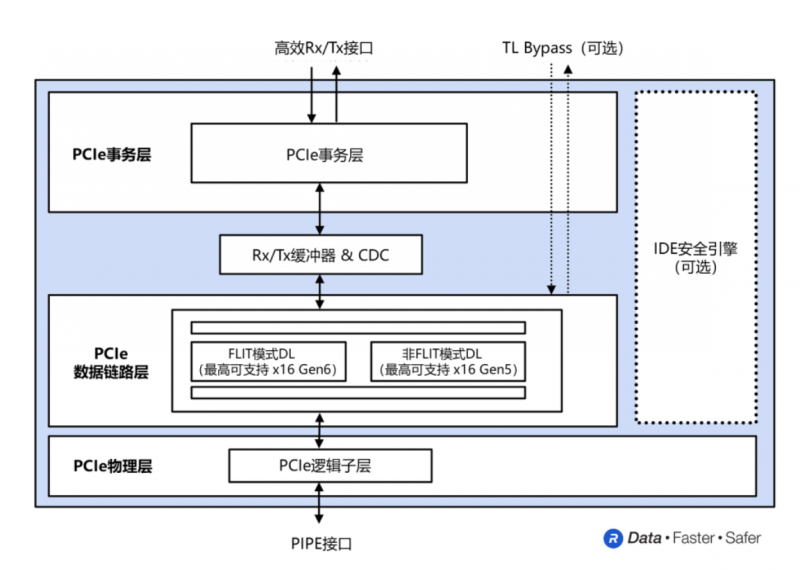

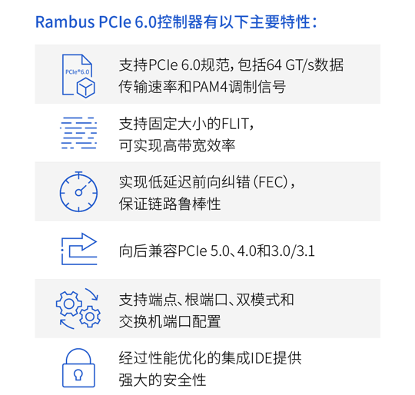

基于最新的PCIe 6.0规范,Rambus推出了控制器产品。在功耗、面积和延时方面进行了优化,可为高性能应用提供高达每秒64GT的数据传输速率,进而推动环保型数据中心的建设,并减少对散热管理的需求,降低拥有成本。

另一方面,该控制器还提供最先进的安全性,其完整性和数据加密(IDE)引擎可以监控和保护PCIe链路免受物理攻击,且无需在此过程中牺牲延迟。

PCIe“左右互搏”走向何方?

左右互搏术让周伯通的武功上升了不止一个档次,那么,PCIe规范的演进又将走向何方?毕竟,从当前PCIe规范的实际商用情况来看,PCIe 5.0的发展以及商业化都尚未进入到最终和成熟阶段。PCIe 6.0尽管从性能和前景都极具吸引力,但是在实际的落地方面能否如期推进?Rambus的PCIe 6.0控制器应用前景又如何?

Matt Jones表示,PCIe 6.0也会经历前一代标准的发展周期。以正式发布于2019年5月的PCIe 5.0来看,如果仅按照当前在数据中心的应用数量来衡量,它是不成熟的,而完全成熟预计会在今年晚些时候到来。不过,从PCIe 5.0过渡到6.0的时间可能比之前几代标准的迭代时间更短,尤其是在企业和数据中心流量持续爆炸式增长的情况下。

他强调,PCIe 4.0/5.0/6.0之间并非一定存在代际竞争,市场上对PCIe 3.0现在仍有较高的需求。对于采用PCIe作为主要接口的解决方案来说,厂商只需要在性能和成本之间做出权衡。

作为推动PCIe 6.0生态所必需的一项早期组成部分,Rambus PCIe 6.0数字控制器目前已经实现量产,AI加速器供应商、I/O和内存供应商等,都可以用它来构建芯片形式的解决方案,并帮助他们的产品在2025年左右进入市场。

Matt Jones表示,他非常兴奋能够面向中国市场正式发布Rambus的PCIe 6.0控制器。以超过400个PCIe控制器的成功生产流片为基础,也再次扩大了Rambus在PCIe IP授权领域的领导地位。希望基于这一产品的发布,随着早期采用其PCIe 6.0控制器的客户推出行业领先的解决方案,能够应对数据流量的增长趋势,并不断促进数据中心的发展。

来源: 与非网,作者: 张慧娟,原文链接: https://www.eefocus.com/article/515684.html

芯耀

芯耀

340

340