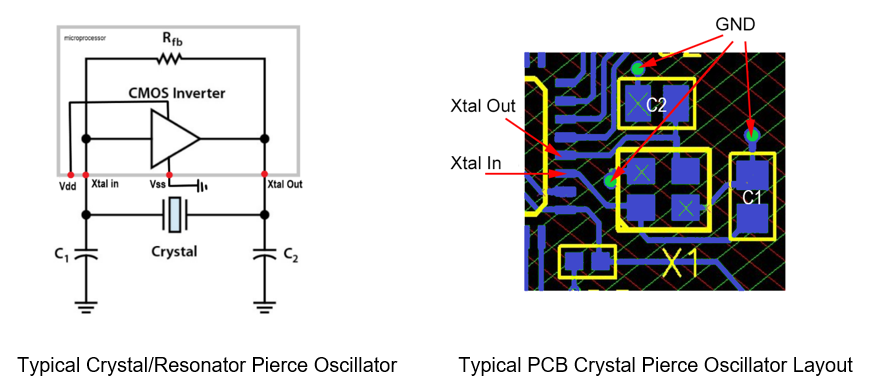

在电子系统设计中,晶振电路的布局是一项关键的工程技术,它影响着系统的稳定性和性能。以下是一些精简而安全的设计原则,以及一些有用的技巧和经验,供您参考。

晶振电路连线精简原则

在设计晶振电路时,应力求连线最短,以减少信号传输的延迟和干扰。简洁的线路布局有助于提高电路的响应速度和抗干扰能力。

晶振电路安全载流原则

在设计铜线时,应确保其尺寸能够安全承载所需电流。铜线的载流能力受线宽、线厚和允许温升等因素的影响。

晶振电路电磁抗干扰原则

为了减少电磁干扰,应采取如下措施:

- 铜膜线的拐弯处应设计为圆角或斜角,避免信号传输中的反射和衰减。

- 双面板上的导线应尽量避免平行走线,以减小寄生耦合。

- 数字地、模拟地和其他类型地线应分开,必要时采用多点接地。

PCB板时钟晶振及相关元件布线原则

一、地线设计原则

- 确保单点和多点接地正确实现。

- 数字地与模拟地应分开。

- 增大接地线的尺寸,以降低接地电位的变化。

- 构成闭环地线,以提高抗噪声能力。

二、配置退耦电容

- 每个集成电路芯片应有一个0.01uf~0.1uf的瓷片电容。

- 对于敏感器件,直接在芯片的电源线和地线之间接入退耦电容。

三、过孔设计

- 合理选择过孔尺寸,以降低寄生效应。

- 使用较薄的PCB板,减小过孔的寄生参数。

- 电源和地线的过孔应尽量靠近元件。

四、降低噪声与电磁干扰的经验

- 选择合适的芯片和组件,以降低噪声。

- 使用满足系统要求的最低频率时钟。

- 时钟应靠近使用该时钟的器件。

印制导线最大允许工作电流

通过计算修正系数、最大温升、覆铜线截面积等因素,确定导线的最大允许工作电流。

环境效应原则与安全工作原则

考虑PCB的应用环境,确保连线和组件能够承受电压峰值和机械应力。

组装方便、规范原则

在设计时要考虑组装的便捷性,例如开窗口便于腐蚀,避免阻焊油遮挡焊盘等。

经济原则

在满足性能要求的前提下,考虑加工成本,如合理选择线宽和过孔尺寸。

热效应原则

通过合理布局器件和印制电路板,以及采用散热措施,确保印制板在工作时不会过热。

综上所述,晶振电路的设计与布局是一个复杂的过程,需要综合考虑多种因素,包括信号完整性、电磁兼容性、热管理以及成本等。遵循上述原则和技巧,有助于设计出高性能、高稳定性的电子系统。

芯耀

芯耀

2149

2149