近年来,以DeepSeek为代表的AI技术突破引发了行业对算力效率的重新思考。传统依赖硬堆算力的模式已显疲态,而算法、芯片、指令与算力的协同优化成为新方向。

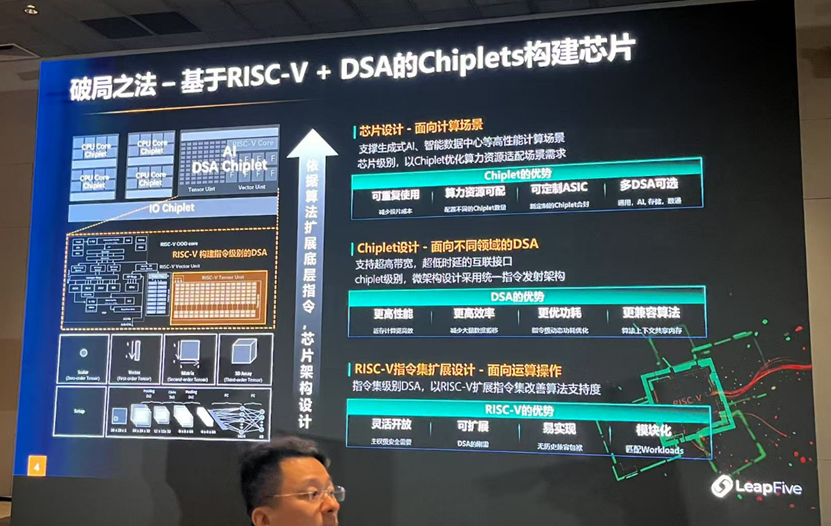

在这一背景下,跃昉科技COO袁博浒在“第五届RISC-V中国峰会” 上表示:“RISC-V指令集与领域专用架构(DSA)的结合,辅以Chiplet技术,正在成为突破摩尔定律限制、重塑全球AI格局的关键路径。”

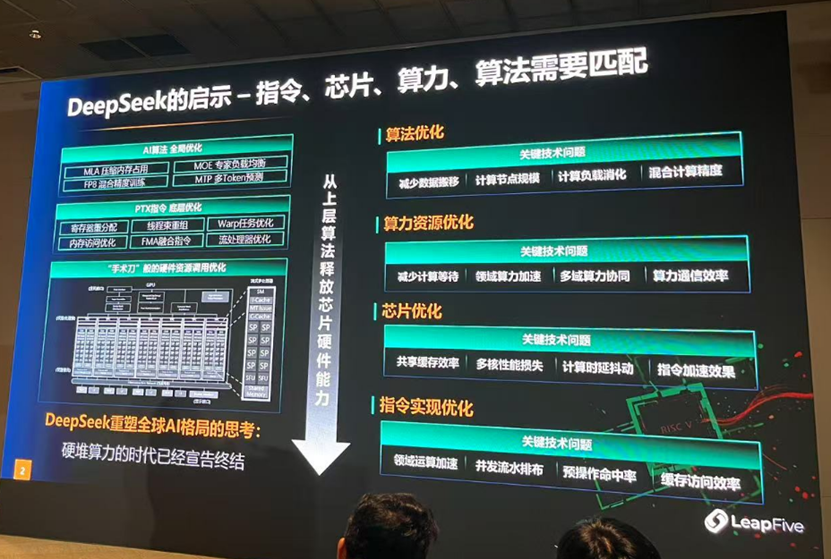

从算法到底层硬件的协同优化

DeepSeek的成功并非偶然,其核心在于通过算法优化最大化释放硬件潜力。例如,通过减少数据流、优化计算节点规模、整合计算精度等算法层面的改进,显著降低了算力需求。这种“自上而下”的设计理念要求芯片架构必须灵活适配算法特性。

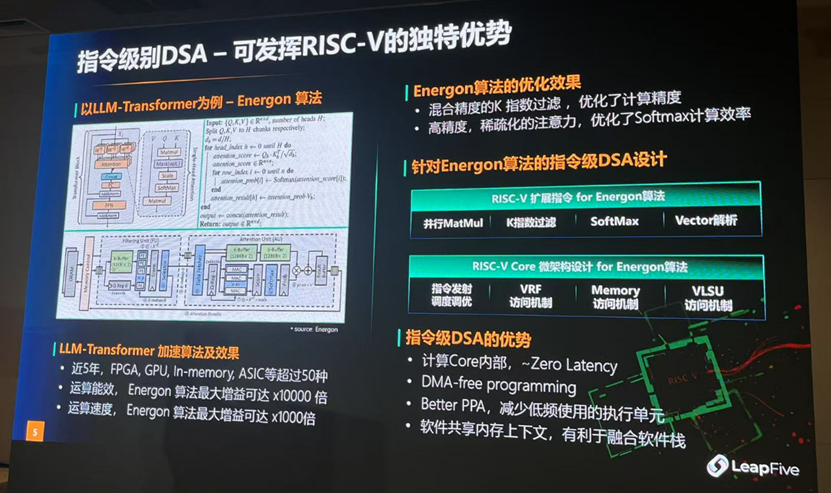

袁博浒认为,RISC-V的开放性与可扩展性可以为此提供理想基础。他指出,RISC-V是目前唯一可根据不同工作负载进行定制的指令集架构,有利于形成“指令”级别的DSA,加速计算。

“以Energon算法为例,通过RISC-V扩展指令集对矩阵乘法(MatMul)、SoftMax等操作进行硬件级加速,可实现高达10000倍的能效提升和1000倍的运算速度增益。这种指令级DSA设计在微架构层面可进一步优化指令发射调度和内存访问机制,实现近乎零延迟的计算效率。” 袁博浒解释道。

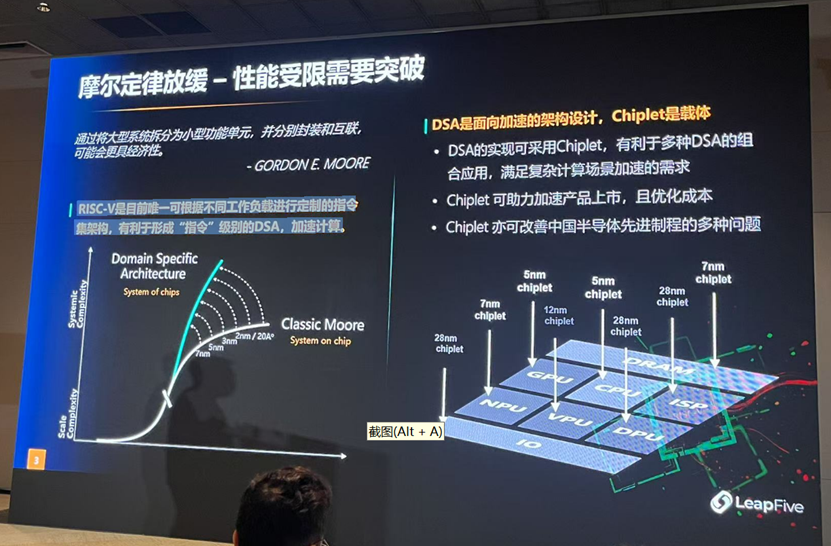

Chiplet与DSA:异构集成的技术突破

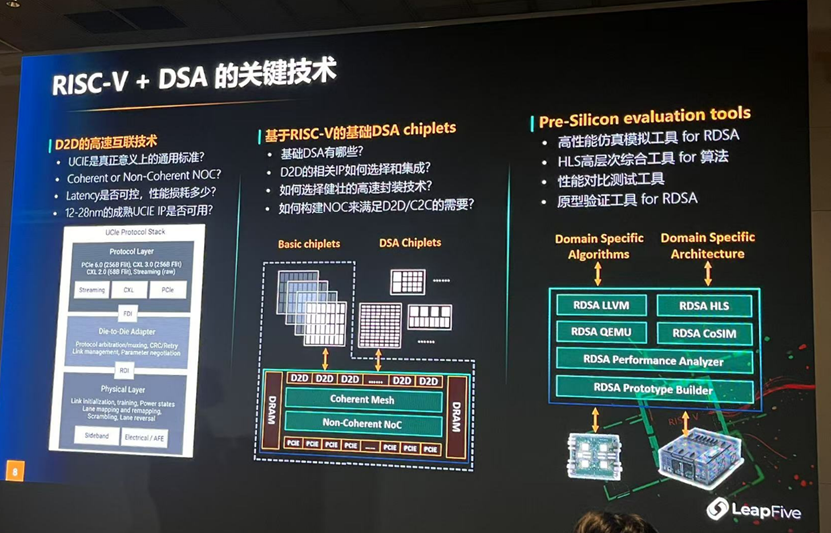

随着摩尔定律放缓,单一制程工艺的性能提升面临瓶颈。DSA架构通过将系统拆分为功能专精的小型单元,结合Chiplet技术实现异构集成,成为解决之道。

例如,在服务器场景中,通用计算(GC-Chiplet)、AI加速(A-Chiplet)、存储(S-Chiplet)等模块可通过高速互联灵活组合,适配多样化负载。这种设计不仅可以提升能效比,还能通过成熟制程(如12-28nm)降低对先进工艺的依赖。

袁博浒提到,UCIe标准的推进正在进一步解决Chiplet互联的互通性问题,而RDSA联盟研发的FlexDLL协议栈和FlexPHY物理层技术,则为国产芯片的异构集成提供了自主可控的底层支持。

据悉,2024年成立的RDSA产业联盟汇聚了全球50余家芯片企业与科研机构,致力于推动RISC-V+DSA+Chiplet的标准化与商业化。联盟不仅建立了D2D高速互联实验室,还通过《芯粒互联接口规范》国家标准的制定,促进国内外技术接轨。

然而,挑战依然存在:UCIe协议的成熟度、多核性能损耗的控制、以及Pre-Silicon仿真工具的完善,仍需产业链持续攻关。

对此,袁博浒透露:“2025年DSA国际创新创业大赛即将启动,面向全球开发者发出挑战——共同攻克能效、安全与可扩展三大关键技术极限。”

写在最后

据Omdia预测,未来DSA芯片市场的50%将集中于数据中心与高性能计算场景。在这一趋势下,RISC-V+DSA架构的模块化特性,使其在AI训练、边缘推理、实时数据处理等领域展现出巨大潜力。

随着跃昉科技等企业推出支持RVA23指令集和硬件虚拟化的高性能模拟器,以及Chiplet交易市场的逐步成型,一个以开放生态为基础、以能效为核心竞争力的算力新时代正在到来。

来源: 与非网,作者: 夏珍,原文链接: https://www.eefocus.com/article/1864607.html

芯耀

芯耀

7519

7519