在很多电路中,系统晶振时钟频率很高,干扰谐波出来的能量也强,谐波除了会从输入与输出两条线导出来外,也会从空间辐射出来,这也导致若PCB中对晶振的布局不够合理,会很容易造成很强的杂散辐射问题,并且一旦产生,很难再通过其他方法来解决,所以在PCB板布局时对晶振和CLK信号线布局非常重要。

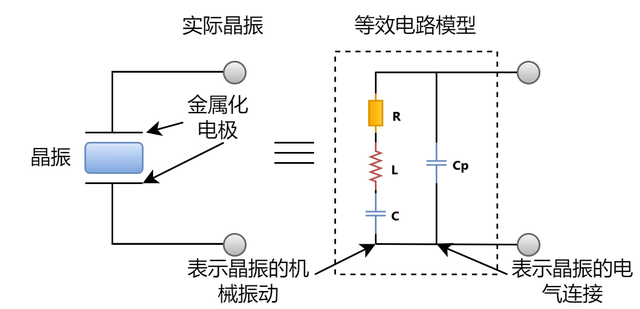

1.晶振的等效电路

事实上,晶振的作用就像一个串联的RLC电路。

晶振的等效电路显示了一个串联的RLC电路,表示晶振的机械振动,与一个电容并联表示与晶振的电气连接,而晶振振荡器便朝着串联谐振运行工作。

其中,R是ESR等效串联电阻,L和C分别是等效电感和电容,Cp为寄生电容。

2. 晶振在PCB板的设计布局

作为数字电路中的心脏,晶振影响着整个系统的稳定性,系统晶振的选择,决定了数字电路的成败。

由于晶振内部存在石英晶体,受到外部撞击等情况造成晶体断裂,很容易造成晶振不起振,所以通常在电路设计时,要考虑晶振的可靠安装,其位置尽量不要靠近板边、设备外壳等地方。PCB对晶振布局时通常注意以下几点:

①晶振不能距离板边太近、晶振的外壳必须接地,否则易导致晶振辐射杂讯。

在板卡设计时尤其需要注意这点。外壳接地可以避免晶振向外辐射,同时可以屏蔽外来信号对晶振的干扰。如果一定要布置在PCB边缘,可以在晶振印制线边上再布一根GND线,同时在包地线上间隔一段距离就打过孔,将晶振包围起来。

②晶振下方不能布信号线,否则易导致信号线耦合晶振谐波杂讯。

保证完全铺地,同时在晶振的300mil范围内不要布线,这样可以防止晶振干扰其他布线、元器件和层的性能。

③若滤波器件放在晶振下方,且滤波电容与匹配电阻未按照信号流向排布,会使滤波器的滤波效果变差。

耦合电容应尽量靠近晶振的电源引脚,按电源流入方向,依容值从大到小顺序摆放。

④时钟信号的走线应尽量简短,线宽大一些,在布线长度和远离发热源上寻找平衡。

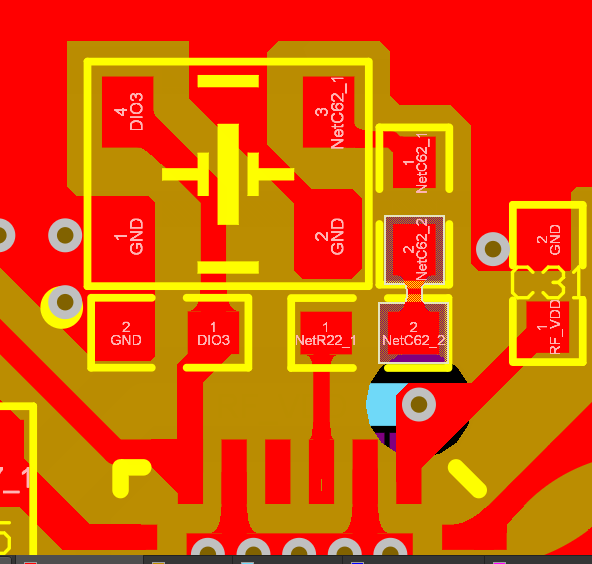

以下图布局为例,晶振的布局方式会相对更优:

②晶振的滤波电容与匹配电阻按照信号流向排布,靠近晶振摆放整齐紧凑。

③晶振靠近芯片处摆放,到芯片的走线尽量短而直。

在电路系统中,高速时钟信号线优先级最高。时钟线是一个敏感信号,频率越高,要求走线尽量简短,以保证信号的失真度达到最小。

芯耀

芯耀

2086

2086