来源:半导体行业观察

作者:anandtech

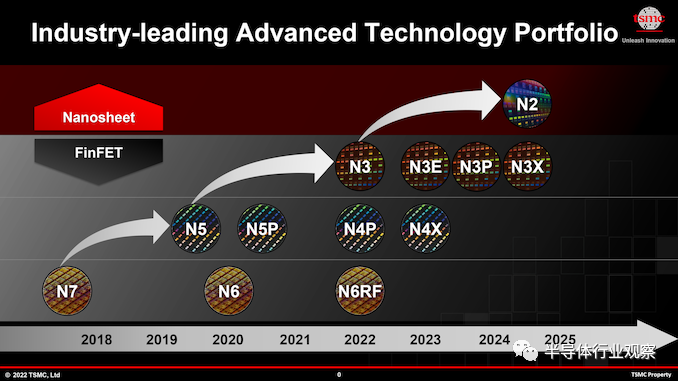

在其 2022 年技术研讨会上,台积电正式公布了其 N2(2 纳米级)制造技术,该技术计划于 2025 年某个时间投入生产,并将成为台积电第一个使用其基于纳米片的栅极全方位场效应的节点晶体管(GAAFET)。新节点将使芯片设计人员能够显著降低其产品的功耗,但速度和晶体管密度的改进似乎不太明显。

台积电的 N2 是一个全新的平台,广泛使用 EUV 光刻技术,并引入了 GAAFET(台积电称之为纳米片晶体管)以及背面供电。新的环栅晶体管结构具有广为人知的优势,例如大大降低了漏电流(现在栅极围绕沟道的所有四个边)以及调节沟道宽度以提高性能或降低功耗的能力. 至于背面电源轨,它通常旨在为晶体管提供更好的电力输送,为后端 (BEOL) 中电阻增加的问题提供解决方案。新的电源传输旨方案在提高晶体管性能并降低功耗。

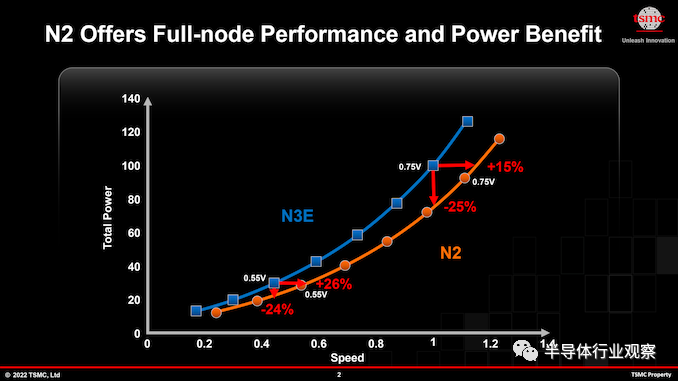

从功能集的角度来看,台积电的 N2 看起来是一项非常有前途的技术。至于实际数字,台积电承诺 N2 将让芯片设计人员在相同功率和晶体管数量下将性能提升 10% 至 15%,或者在相同频率和复杂度下将功耗降低 25% 至 30%,同时,与N3E 节点相比,芯片密度增加了 1.1 倍以上。

与 N3E 相比,台积电 N2 节点带来的性能提升和功耗降低与代工厂的新节点通常带来的效果一致。但所谓的芯片密度提升(应该反映晶体管密度增益)仅略高于 10% ,这并不是特别鼓舞人心,特别是考虑到与普通 N3 相比,N3E 已经提供了略低的晶体管密度。

请记住,如今 SRAM 和模拟电路几乎无法扩展,因此这些天可能会预期实际芯片的晶体管密度会出现平庸的改进。然而,对于 GPU 和其他基于晶体管数量快速增加而生死攸关的芯片而言,三年内芯片密度大约提高 10% 肯定不是好消息。

当台积电的 N2 投入生产时,该公司还将拥有密度优化的 N3S 节点,看来代工厂将拥有两种基于不同类型晶体管的工艺技术,但提供非常相似的晶体管密度,这在以前从未发生过。

像往常一样,台积电将为其 N2 节点提供各种功能和选择,以允许芯片设计人员针对移动和高性能计算设计等进行优化(请注意,台积电将 HPC 称为非移动、汽车或专业的一切。包括从低功耗笔记本电脑 CPU 到针对超级计算机的高端计算 GPU)。

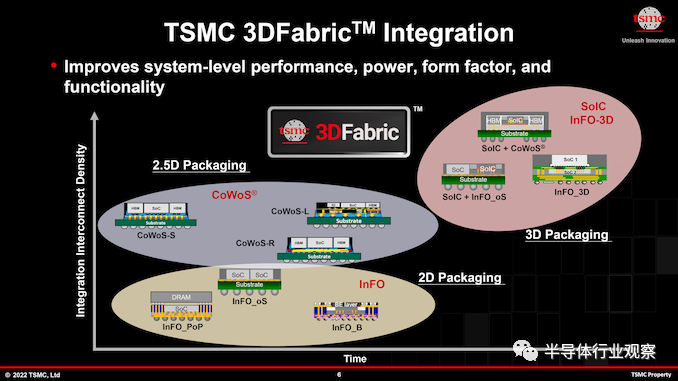

此外,平台产品包括台积电称之为“chiplet integration”的东西,这可能意味着台积电使其客户能够轻松地将 N2 芯片集成到使用各种节点制造的multi-chiplet封装中。由于晶体管密度扩展正在放缓并且新工艺技术的使用成本越来越高,因此multi-chiplet封装将在未来几年变得更加普遍,因为开发人员将使用它们来优化他们的设计和成本。

台积电预计会在 2024 年下半年开始使用其 N2 制造工艺风险试产,这意味着该技术应该在 2025 年下半年可用于商业产品的大批量制造 (HVM)。但是,考虑到现代半导体生产周期的长度,如果一切按计划进行,预计第一批 N2 芯片将在 2025 年末或 2026 年上市可能更为务实。

未来三年,五种3nm工艺

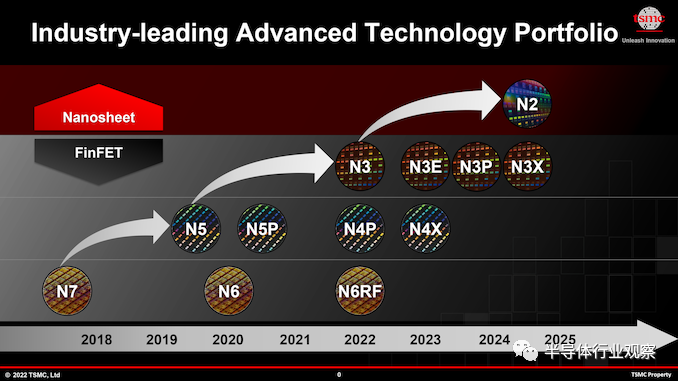

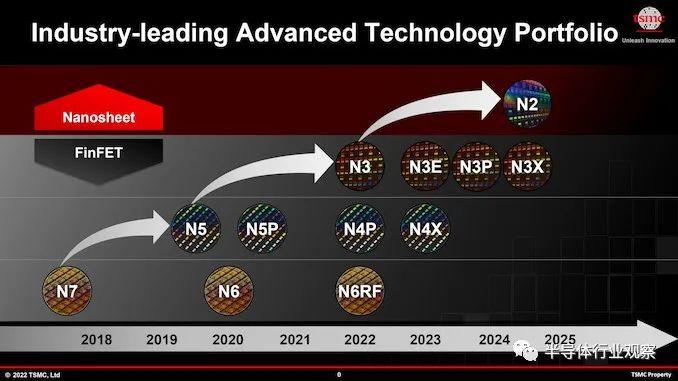

在技术研讨会上,台积电宣布的关键事项之一是其属于其 N3(3 纳米级)和 N2(2 纳米级)系列的领先节点,这些节点将在未来几年用于制造先进的 CPU、GPU 和 SoC .

- N3:未来三年的五个节点

随着制造工艺变得越来越复杂,它们的寻路、研究和开发时间也变得越来越长,因此我们不再看到台积电和其他代工厂每两年就会出现一个全新的节点。在 N3 中,台积电的新节点引入节奏将扩大到 2.5 年左右,而在 N2 中,它将延长到 3 年左右。

这意味着台积电将需要提供 N3 的增强版本,以满足其客户的需求,这些客户仍在寻求每瓦性能的改进以及晶体管密度每年左右的提升。台积电及其客户需要多个版本的 N3 的另一个原因是,代工厂的 N2 依赖于使用纳米片实现的全新栅极环绕场效应晶体管 (GAA FET),预计这将带来更高的成本、新的设计方法、新 IP 和许多其他变化。虽然尖端芯片的开发人员将很快转向 N2,但台积电的许多普通客户将在未来几年坚持使用各种 N3 技术。

在其 2022 年台积电技术研讨会上,该代工厂谈到了将在未来几年推出的四种 N3 衍生制造工艺(总共五个 3 纳米级节点)——N3E、N3P、N3S 和 N3X。这些 N3 变体旨在为超高性能应用提供改进的工艺窗口、更高的性能、增加的晶体管密度和增强的电压。所有这些技术都将支持 FinFlex,这是 TSMC 的“秘密武器”功能,极大地增强了他们的设计灵活性,并允许芯片设计人员精确优化性能、功耗和成本。

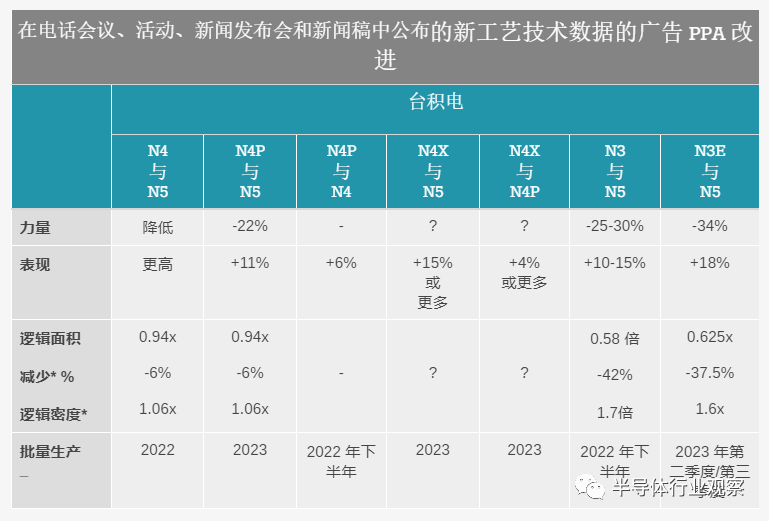

*请注意,台积电在 2020 年左右才开始分别发布针对模拟、逻辑和 SRAM 的晶体管密度增强。其中一些数字仍然反映了由 50% 逻辑、30% SRAM 和 20% 模拟组成的“混合”密度

- N3 和 N3E:HVM 步入正轨

台积电的第一个 3 纳米级节点称为 N3,该节点有望在今年下半年开始大批量制造 (HVM)。实际芯片将于 2023 年初交付给客户。该技术主要针对早期采用者(如Apple 等),他们可以投资于领先的设计,并从前沿节点提供的性能、功率和面积 (PPA) 中受益。但由于它是为特定类型的应用量身定制的,因此 N3 的工艺窗口相对较窄(产生确定结果的一系列参数),就良率而言,它可能并不适合所有应用。

- 这就是 N3E 发挥作用的时候。

新技术提高了性能,降低了功耗,增加了工艺窗口,从而提高了良率。但权衡是该节点的逻辑密度略有降低。与 N5 相比,N3E 将提供 34% 的功耗降低(在相同的速度和复杂性下)或 18% 的性能提升(在相同的功率和复杂性下),并将逻辑晶体管密度提高 1.6 倍。

值得注意的是,根据台积电的数据,N3E 将提供比 N4X更高的时钟速度 (2023 年到期)。不过后者也将支持超高驱动电流和1.2V以上的电压,在这一点上它将能够提供无与伦比的性能,但功耗非常高。

总的来说,N3E 看起来是比 N3 更通用的节点,这就是为什么台积电在这一点上拥有更多的“3nm 流片”,而不是在其类似的开发阶段拥有 5nm 级节点也就不足为奇了.

使用 N3E 的芯片的风险生产将在未来几周(即 2022 年第二季度或第三季度)开始,HVM 将在 2023 年中期开始(同样,台积电没有透露我们是在谈论第二季度还是第三季度)。因此,预计商业 N3E 芯片将在 2023 年底或 2024 年初上市。

- N3P、N3S 和 N3X:性能、密度、电压

N3 的改进并不止于 N3E。台积电将在 2024 年左右的某个时间推出 N3P,这是其制造工艺的性能增强版本,以及 N3S,该节点的密度增强版本。不幸的是,台积电目前没有透露这些变体将提供哪些改进到基线 N3。事实上,此时台积电在其路线图的所有版本中甚至都没有展示 N3S,因此尝试猜测其特性确实不是一个好生意。

最后,对于那些无论功耗和成本都需要超高性能的客户,台积电将提供N3X,它本质上是N4X的意识形态接班人。同样,台积电没有透露有关该节点的详细信息,只是表示它将支持高驱动电流和电压。我们可能会推测 N4X 可以使用背面供电,但由于我们谈论的是基于 FinFET 的节点,而台积电只会在基于纳米片的 N2 中实现背面供电轨,我们不确定情况是否如此。尽管如此,在电压增加和性能增强方面,台积电可能有许多优势。

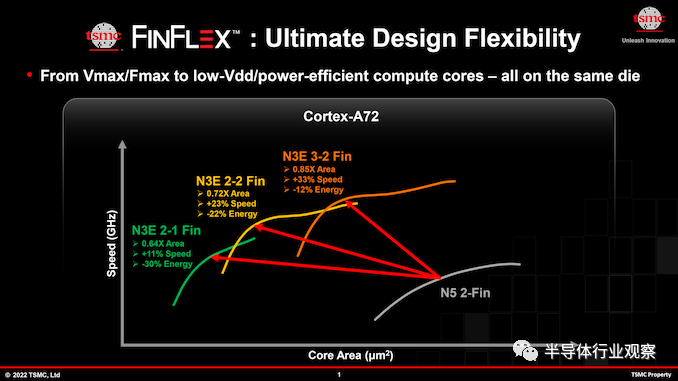

- FinFlex:N3 的秘诀

说到增强功能,我们绝对应该提到台积电 N3 的秘诀:FinFlex 技术。简而言之,FinFlex 允许芯片设计人员精确地定制他们的构建模块,以实现更高的性能、更高的密度和更低的功耗。

当使用基于 FinFET 的节点时,芯片设计人员可以在使用不同晶体管的不同库之间进行选择。当开发人员需要以性能为代价来最小化裸片尺寸并节省功耗时,他们会使用双栅极单鳍 (2-1) FinFET(见图)。但是,当他们需要在芯片尺寸和更高功率的权衡下最大限度地提高性能时,他们会使用三栅极双鳍 (3-2) 晶体管。当开发人员需要平衡时,他们会选择双栅极双鳍 (2-2) FinFET。

目前,芯片设计人员必须为整个芯片或 SoC 设计中的整个模块坚持一种库/晶体管类型。例如,可以使用 3-2 个 FinFET 来实现 CPU 内核以使其运行更快,或者使用 2-1 个 FinFET 来降低其功耗和占用空间。

这是一个公平的权衡,但它并不适用于所有情况,尤其是当我们谈论使用比现有技术更昂贵的 3 纳米级节点时。

对于 N3,台积电的 FinFlex 技术将允许芯片设计人员在一个模块内混合和匹配不同类型的 FinFET,以精确定制性能、功耗和面积。对于像 CPU 内核这样的复杂结构,这样的优化提供了很多提高内核性能的机会,同时仍然优化了裸片尺寸。因此,我们渴望看到 SoC 设计人员将如何在即将到来的 N3 时代利用 FinFlex。

FinFlex 不能替代节点专业化(性能、密度、电压),因为工艺技术比单一工艺技术中的库或晶体管结构有更大的差异,但 FinFlex 看起来是优化性能、功率和成本的好方法台积电的 N3 节点。最终,这项技术将使 FinFET 的灵活性更接近基于纳米片的 GAAFET 的灵活性,后者将提供可调节的通道宽度,以获得更高的性能或降低功耗。

与台积电的 N7 和 N5 一样,N3 将成为世界上最大的半导体对比度制造商的另一个持久节点系列。尤其是随着台积电在 2nm 阶段转向基于纳米片的 GAAFET,3nm 系列将成为该公司“经典”前沿 FinFET 节点的最后一个系列,许多客户将坚持使用几年(或者更多)。

反过来,这也是台积电为不同应用准备多个版本的 N3 以及 FinFlex 技术的原因,以便为芯片设计人员的设计提供一些额外的灵活性。

首批 N3 芯片将在未来几个月内投入生产,并于 2023 年初上市。同时,台积电在 2025 年推出 N2 工艺技术后,仍将继续使用其 N3 节点生产半导体。

成熟产能扩产50%

台积电今天下午透露,到 2025 年,其成熟和专业节点的产能将扩大约 50%。该计划包括在中国台湾、日本和中国大陆建设大量新晶圆厂。此举将进一步加剧台积电与格芯、联电、中芯国际等芯片代工厂商之间的竞争。

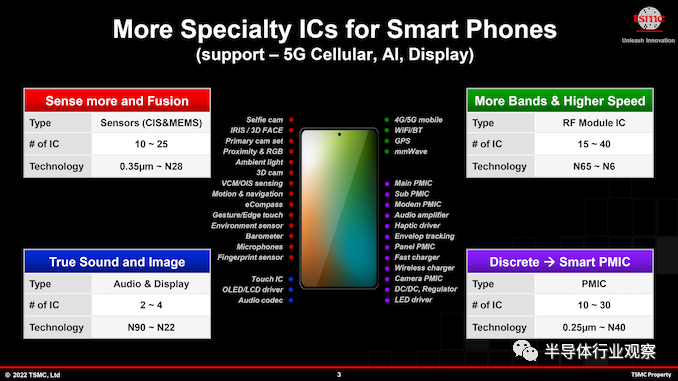

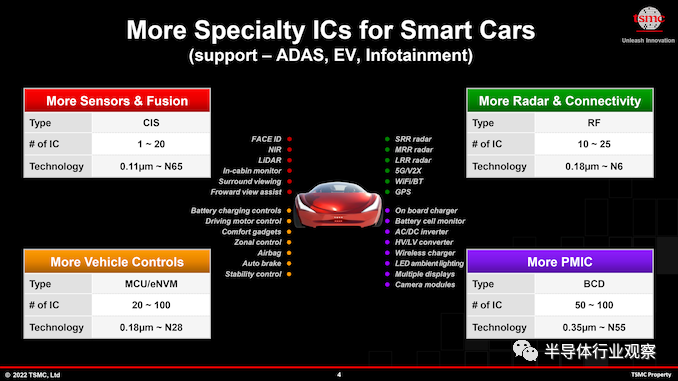

当我们在 AnandTech 谈论硅光刻技术时,我们主要介绍用于生产先进 CPU、GPU 和移动 SoC 的前沿节点,因为这些都是推动进步的设备。但是有数百种设备是基于成熟或专业的工艺技术制造的,这些设备与那些复杂的处理器一起使用,或者为对我们的日常生活产生重大影响并且近年来变得越来越重要的新兴智能设备提供动力。

近年来,各种计算和智能设备的需求激增,引发了全球芯片供应危机,进而影响到汽车、消费电子、PC和众多相邻行业。

现代智能手机、智能家电和个人电脑已经使用了数十种芯片和传感器,而这些芯片的数量(和复杂性)只会越来越多。这些零件使用更先进的专业节点,这也是台积电等公司必须扩大原本“旧”节点的产能以满足未来几年不断增长的需求的原因之一。

但还有另一个市场即将爆发:智能汽车。汽车已经使用了数百个芯片,汽车的半导体含量也在不断增长。据估计,几年后每辆汽车的芯片数量将达到 1,500 个左右——而且必须有人制造它们。这就是为什么台积电的竞争对手 GlobalFoundries 和中芯国际在过去几年一直在增加对新产能的投资。

台积电在半导体行业拥有最大的资本支出预算(仅受到三星的挑战),近年来对其成熟和专业的节点生产计划相对安静。但在 2022 年台积电技术研讨会上,该公司正式概述了其计划。

该公司正在为成熟和专业节点投资四个新设施:

- 位于日本熊本的Fab 23 第一期 。该半导体制造工厂将使用台积电的 N12、N16、N22 和 N28 节点制造芯片,并将拥有每月高达 45,000 片 300 毫米晶圆的生产能力。

- 中国台湾台南 Fab 14 第 8 期。

- 中国台湾高雄 Fab 22 二期。

- 位于中国南京的 Fab 16 1B 期。台积电目前在中国生产其 N28 芯片,不过曾有传言称新阶段能够使用更先进的节点制造芯片。

在未来三年内将成熟/专业化产能提高 50% 对公司来说是一个重大转变,这将提高台积电在市场上的竞争地位。或许更重要的是,该公司的专业节点主要基于其通用节点,这允许至少一些公司将他们曾经为计算或 RF 开发的 IP 重新用于新应用程序。

“[我们的] 专业技术非常独特,因为它基于通用技术平台 [逻辑技术平台],因此我们的独特策略是让我们的客户共享或重用许多 [通用] IP,”台积电业务发展副总裁、高级工程师 Kevin Zhang 说。“例如,你有射频能力,你在通用逻辑平台上构建射频,但后来你发现'嘿,有人需要所谓的 ULV 功能来支持物联网产品应用。' 您想在一个通用平台上构建它,这样您就可以允许不同的产品线能够全面共享 IP,这对我们的客户非常重要,因此我们确实希望提供一个集成平台来满足客户的市场需求产品视角。

还有其他优点。例如,台积电的 N6RF 允许芯片设计人员将高性能逻辑与 RF 相结合,从而使他们能够构建调制解调器等产品和其他更独特的解决方案。许多公司已经熟悉 TSMC 的 N6 逻辑节点,因此现在他们有机会将 RF 连接添加到受益于高性能的产品中。GlobalFoundries 也有类似的做法,但由于美国的代工厂没有任何东西可以与台积电的 N6 相提并论,因此台积电在这方面具有无可争辩的优势。

凭借其成熟节点和专业技术的通用平台方法,以及增加 50% 的容量,台积电将能够在未来几年为全球提供更多用于智能和连接设备的芯片。此外,它还将通过显著增加公司来自成熟和专业节点的收入以及增加对竞争对手的压力来使台积电受益。

2024年引入High NA EUV光刻机

台积电高管周四表示,这家全球最大的芯片制造商将在 2024 年拥有下一个版本的 ASML Holding NV 最先进的芯片制造工具。

这种名为“high-NA EUV”的工具产生聚焦光束,在用于手机、笔记本电脑、汽车和人工智能设备(如智能扬声器)的计算机芯片上创建微观电路。EUV 代表极紫外,即 ASML 最先进机器使用的光波长。

“台积电将在 2024 年引入高 NA EUV 扫描仪,以开发客户所需的相关基础设施和图案化解决方案,以推动创新,”台积电研发高级副总裁 YJ Mii 在硅谷举行的台积电技术研讨会上表示。

Mii没有透露该设备何时用于大规模生产,该设备是用于制造更小更快芯片的第二代极紫外光刻工具。台积电的竞争对手英特尔公司表示,它将在 2025 年之前将这些机器投入生产,并且它将是第一家收到该机器的公司。

随着英特尔进入其他公司设计的芯片制造业务,它将与台积电竞争这些客户。

台积电业务发展高级副总裁张凯文澄清说,台积电不会在 2024 年准备好使用新的High NA EUV 工具进行生产,但它将主要用于与合作伙伴的研究。

“台积电在 2024 年拥有它的重要性意味着他们可以更快地获得最先进的技术,”参加研讨会的 TechInsights 的芯片经济学家 Dan Hutcheson 说。

“High-NA EUV 是技术的下一个重大创新,它将使芯片技术处于领先地位,”Hutcheson 说。

芯耀

芯耀

336

336

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)