一辆载着印有“ASML”LOGO保护箱的卡车驶入美国俄勒冈州(Oregon)的英特尔希尔斯伯勒(Hillsboro)园区。箱身上绑着红绳,并系了蝴蝶结,里面是荷兰ASML研制出的全球首台高数值孔径极紫外光刻机(High NA EUV)的一部分。

这是目前唯一能够实现2nm工艺的光刻机,它的交付,意味着全球范围内的芯片“制程大战”将会进入2nm阶段。在当前台积电领先、英特尔和三星加紧追赶的晶圆制造格局中,不论是想保持领先,还是想弯道超车,都将2nm视为竞争的“致命武器”。2nm果真能堪此重任么?随着2nm之战越来越近,有必要厘清业界的2nm情结。

得ASML者得2nm?

“如果单讨论2nm工艺的实现,毫无疑问,ASML的0.55数值孔径EUV光刻机是一切的先决条件。”业内专家莫大康告诉《中国电子报》记者。

从纵向的晶圆生产流程来看,设备与硅片是晶圆生产活动的起点,优先级高于光刻胶以及其他应用于生产过程中的气体材料。设备升级是实现2nm工艺节点飞跃的必要条件,而材料升级是锦上添花的部分。

从横向的平替设备来看,极紫外光刻是成熟度最高的方式。在极紫外光刻之外,佳能全力押注纳米压印技术。不同于将光照直接打在掩模版上,并通过透镜最终折射在晶圆上的极紫外光刻,纳米压印是将电路图形通过“盖章”的方式压在晶圆上的一种技术路径。佳能CEO御手洗富士夫曾表示,纳米压印单次光刻工序的成本为传统光刻成本的二分之一。虽然纳米压印具有成本优势,但是由于其工艺存在一定特殊性,且对于制造环境的要求很高,加之当前还未出现量产的成功案例,想要通过纳米压印实现2nm还需时间检验。

2nm与EUV设备高度绑定,这几乎是不争的事实。因此,几家晶圆代工企业必须和世界唯一的光刻机设备厂商ASML“搞好关系”。

1987年,台积电刚刚成立,ASML还是飞利浦旗下的一家小公司。飞利浦以芯片技术换取了台积电27.5%的股份。1988年,台积电因为厂房遭遇大火,向ASML一口气订购了17台光刻机,两家企业从此建立联系。在之后数十年的岁月中,ASML的新设备都会交付给台积电,而台积电也会将在晶圆厂积累的数据反馈给ASML。

2012年,三星以363亿韩元购买了ASML3%的股份。2023年12月,三星电子董事长李在镕随韩国总统尹锡悦访问ASML总部,并宣布将与ASML共同投资1万亿韩元在韩国建立研究中心。

日本建立不久的Rapidus也频繁向ASML示好,并派遣员工进入ASML学习,足以见其对光刻设备的重视。

英特尔早在2022年1月就宣布向ASML发出了第一份采购订单,约定购买后者0.55数值孔径的EUV光刻机。2024年,随着ASML的订单陆续交付给芯片制造厂和IDM,2nm将会进入“竞速赛”的阶段。

高良率量产是道坎?

先做出2nm意味着立于不败之地吗?答案当然是否定的。产业界关注的并非2nm的生产,而是量产。早在2021年5月,IBM就已经通过多重曝光技术实现了2nm工艺,这也是日本Rapidus派员去IBM学习其先进技术的主要原因。但是IBM的成果科研属性强于商业属性,换言之,它既没有能够生产2nm制程的光刻机,同时也不具备其他芯片制造厂量产2nm的资金和生产线,也就无法应对未来持续增长的先进制程的需求。

量产之外,还有良率的问题需要晶圆厂考虑。

以目前台积电和三星的3nm为例,其良率基本在60%-70%浮动,而如果到2nm阶段,良率只可能更低。

“影响良率主要有三个因素,一是刻蚀精度,这个通过设备可以有效解决;二是硅片的缺陷密度,它与加工过程及材料等有关。”莫大康表示,“重要的是随着制程的升级,过小的尺寸容易伴生量子隧穿效应,甚至是漏电现象。这会导致许多随机误差的出现,而晶圆厂凭借现有技术,也很难在短时间内定位和消磨这些随机性极强的误差。”

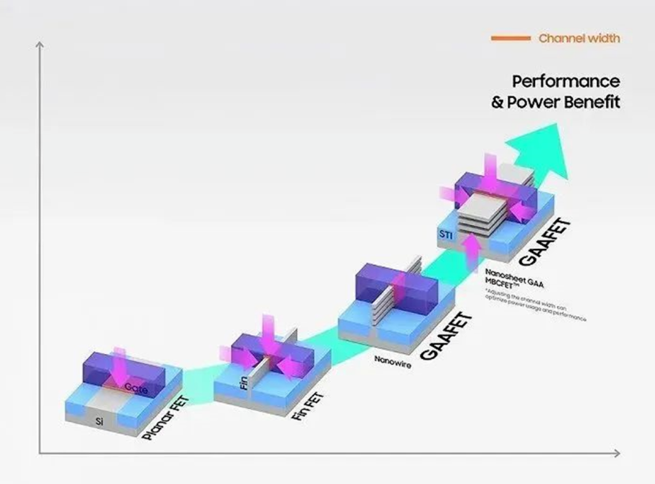

目前,三星电子采用了GAA架构来防止背面漏电,以求提升3nm的良率。英特尔在20A制程上采用了RibbonFET架构,功能与GAA相似,这也是被视作在为未来的18A制程进行技术积累。而台积电3nm仍然使用FinFET架构,转为GAA架构可能要等到2nm之后。

三星电子晶体管结构路线图(图片来源:三星电子)

不论是实现量产,还是通过新架构提升良率,背后都牵扯到2nm的制造成本问题。

对于晶圆厂而言,量产2nm所需的设备成本和研发成本将一路走高,性价比则会降低。机构预测,2nm晶圆片的价格约3万美元,比3nm要贵50%。同时,由于良率较3nm更低,这将使晶圆厂承担更多的次品压力。

据悉,苹果在3nm订单中只向台积电支付了质量达标的那部分晶圆费用,进入2nm阶段后,台积电将不可避免承担更大比例的次品成本。

虽然2nm无法为晶圆厂带来立竿见影的经济收益,但从长期来看,率先实现2nm能够带来良好的品牌效益。

什么左右客户的选择?

芯片做得好不好最终还是以客户的订单量为准。而除了芯片本身的产量、良率、价格因素之外,客户还有两方面的顾虑。

一方面,越发先进的制程工艺带来的不确定性增加了终端厂商的试错成本。

苹果是一家乐于“吃螃蟹”的企业。2023年,苹果A17芯片率先采用了台积电3nm工艺,而在同时期发布的高通骁龙8Gen3和联发科天玑9300则采用台积电4nm工艺。在智能手机市场,制程工艺逐渐成为终端厂商差异化竞争的指标之一,苹果也将“率先使用最先进工艺”视作自身产品的一大卖点。

然而,在3nm中拔得头筹的苹果在消费者实际使用中却出现了发热现象,除了iPhone15所使用的钛金属手机外壳之外,也可能与台积电3nm未使用GAA架构有关。

另一方面,长久的深度合作拉高了终端厂商的技术迁移难度。

“这是工艺黏性的问题。芯片设计企业选择某家代工厂,代表着双方之间的技术融合已经成功,而如果此时调换到其他代工厂,就意味着IP、EDA等技术都需要重新磨合,这要花费很长时间,同时由于制程越来越先进,迁移带来的风险也越大。”莫大康表示。

目前,苹果、英伟达、高通、AMD等设计企业都与台积电建立了深度绑定的合作生态。根据台积电2023年第三季度财报,智能手机和HPC领域的订单占据了81%的营收占比。其中,智能手机领域环比增长率更是高达33%。

台积电2023年第三季度各平台营收情况(图片来源:台积电)

苹果与台积电的合作已有十余年,长期深度的合作关系无形中提升了客户的迁移成本。不过,各芯片设计企业也在尝试将产能需求分散给多家代工厂,以此削弱长期合作带来的工艺黏性。

英伟达不止一次在公开场合透露了自己与英特尔合作的意愿。在2023年12月,英伟达首席财务官Colette Kress在接受采访时表示:“台积电一直是出色的公司,我们也请了三星代工相关芯片,当然,我们乐意见到第三家。”而高通目前虽由台积电独家代工,也在观望三星电子在GAA架构不断磨合之下的良率提升效果。

在2nm的竞争中,英特尔已经获得了拥有首台高数值孔径EUV光刻机先机;台积电既有3nm量产经验,又有长期以来与客户维持的紧密联系;三星电子手握GAA架构,不仅频繁释放良率提升的信号,还传出今年第一季度其代工业务将降价10%-15%。未来的2nm之争,以光刻机为起点,最后还是要落在客户对高良率产品的信任之上。

芯耀

芯耀

1044

1044

下载ECAD模型

下载ECAD模型