名称:数字钟设计VHDL代码Quartus仿真

软件:Quartus

语言:VHDL

代码功能:

数字钟设计

内容:

在FPGA上设计一个时钟控制器。在4位8段数码管上,实现小时(00-23)和分钟(00...59)的计时和显示。FPGA时钟1MHz。采用动态扫描方式驱动4个数码管。FPGA时钟1MHz。

时钟显示形式为:

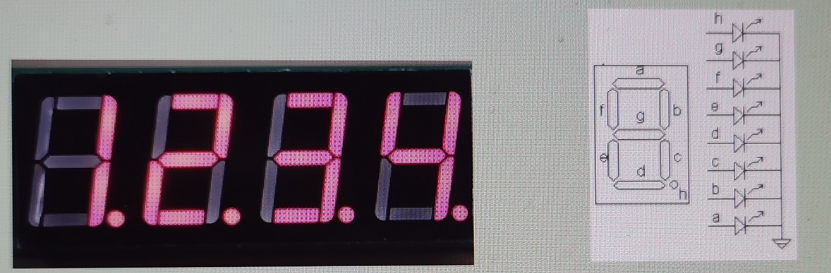

共使用4个8段数码管,如图上图所示。设从左到右为1234位。显示规则如下:

(1)第1、2位为小时。第1位的小点不显示;第2位的小点持续显示。

(2)第3、4位为分钟。第3位的小点不显示;第4位的小点以1秒为周期闪烁。

重点:

1、分频获得秒时钟

2、了解数码管动态扫描的驱动申路动态扫描有多种驱动方式,请自行设计电路,且FPGA的输出能配合该驱动方式。

3、动态扫描还需要一个扫描时钟,要保证每个数码管刷新频率超过24H也不要太高。

4、思考如何实现两位的十进制数显示。

加分设计:

整点报时(采用蜂鸣器)

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

演示视频:

设计文档:

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. 仿真图

5.1 整体仿真

5.2 分频模块

5.3 计时模块

5.4 整点报时模块

5.5 显示模块

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY Digital_clock IS PORT ( clk_1M : IN STD_LOGIC;--1MHz bell_out : OUT STD_LOGIC;--整点报时蜂鸣器 bit_select : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END Digital_clock; ARCHITECTURE trans OF Digital_clock IS --模块声明 COMPONENT Bell IS PORT ( clk_1M : IN STD_LOGIC; hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bell_out : OUT STD_LOGIC ); END COMPONENT; COMPONENT display IS PORT ( clk : IN STD_LOGIC; hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bit_select : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END COMPONENT; COMPONENT fenping IS PORT ( clk_1M : IN STD_LOGIC; clk_1Hz : OUT STD_LOGIC ); END COMPONENT; COMPONENT jishi IS PORT ( clk_1M : IN STD_LOGIC; clk_1Hz : IN STD_LOGIC; hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT;

点击链接获取代码文件:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=1249

芯耀

芯耀

1029

1029