当韩国2月半导体出口暴增134%、SK海力士HBM产能排至2027年、车规芯片失效率要求逼近0ppm时,很少有人注意到一个细节:所有这些高端芯片在出厂前,都必须在烧录环节完成“最后的验证”。这个曾经被视为“简单写入”的工序,正在经历一场从离线编程到产线智能体的深刻变革。

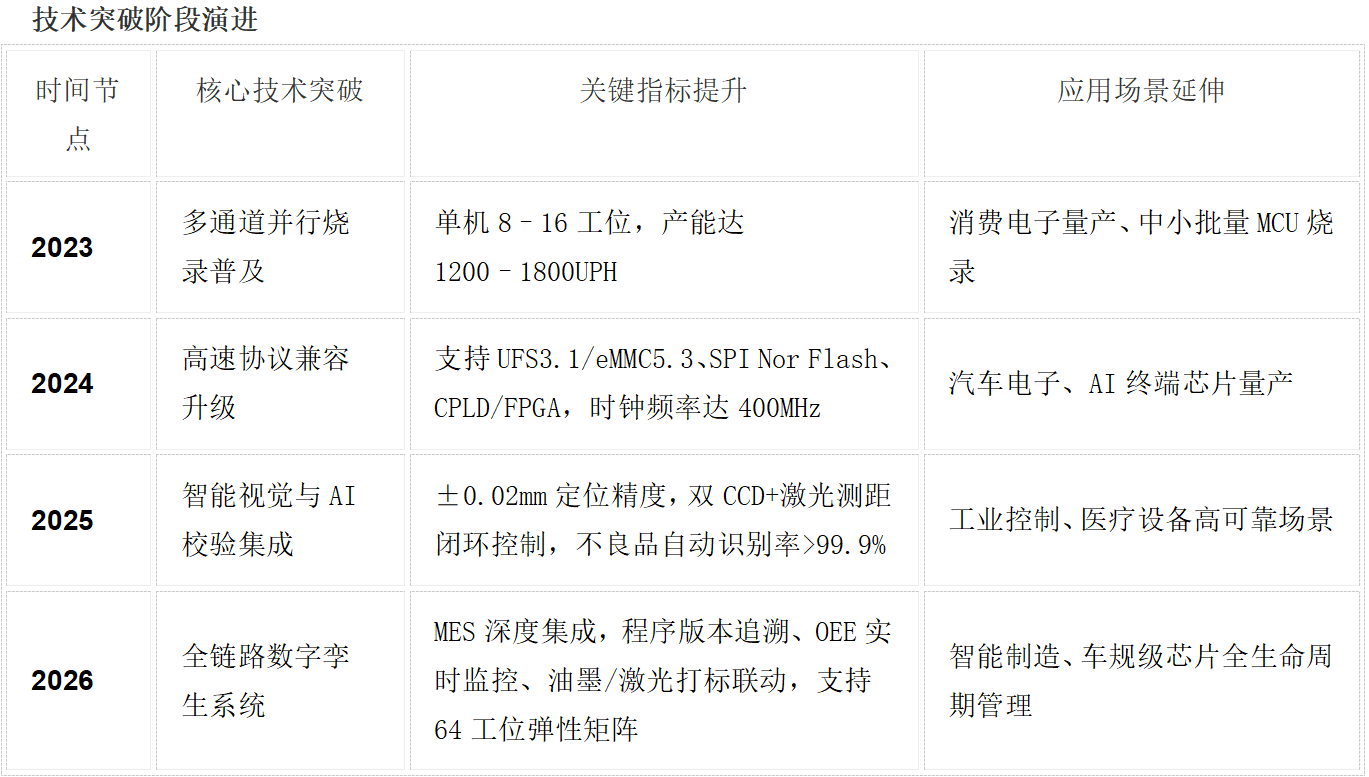

过去四年,芯片烧录技术的演进路线清晰地反映出半导体产业对效率、精度和可靠性的极致追求。从多通道并行到高速协议兼容,从AI视觉校验到全链路数字孪生,每一次技术迭代都踩中了产业需求的脉搏。

01 趋势洞察:芯片复杂度攀升,倒逼烧录技术升级

根据世界半导体贸易统计组织(WSTS)数据,2025年全球半导体市场规模达7720亿美元,同比增长22.5%,其中存储芯片和车规级芯片是主要增长引擎。TrendForce预测,2026年第一季度NAND闪存合约价将上涨55%-60%,服务器DRAM涨幅接近90%。

芯片性能提升的同时,复杂度也在指数级增长。以车规级MCU为例,单颗芯片代码量从2018年的数MB增至如今的数百MB,存储接口从SPI演进至eMMC、UFS,时钟频率从几十MHz飙升至400MHz级别。传统离线编程方式已无法满足量产效率和质量追溯的要求,烧录环节的智能化升级成为必然。

高盛报告指出,2026年全球DRAM供需缺口达4.9%,为15年来最严重短缺水平。在产能紧张的背景下,每一颗芯片的利用率都被推至极限,烧录设备的稳定性、精度和协同能力,直接影响芯片制造商的整体良率和交付能力。

02 技术挑战:四大瓶颈制约后端效率

瓶颈一:产能爬坡压力。 2023年存储市场尚处去库存周期,烧录设备主流配置为单机8-16工位,产能1200-1800UPH。但进入2024年,AI服务器对HBM和高速DRAM需求爆发,消费电子存储配置升级,单机产能开始吃紧。SK海力士近日坦言“今年无法满足所有客户需求”,这意味着后端设备必须同步提升效率。

瓶颈二:高速协议适配滞后。 UFS4.1接口理论带宽达5800MB/s,是前代两倍以上;eMMC5.3、LPDDR5X等新标准相继商用,对烧录设备的协议栈兼容性提出严苛要求。据半导体行业观察报道,通用烧录器在处理新协议时往往需要数月算法开发周期,难以满足客户快速量产需求。

瓶颈三:高可靠性场景的质量门槛。 汽车电子、医疗设备对芯片烧录的可靠性要求近乎苛刻。国际汽车电子协会AEC-Q100标准要求车规芯片失效率低于1ppm(百万分之一),传统烧录设备依赖人工目检或简单电气校验,误判率难以满足要求。2025年,行业开始引入智能视觉与AI校验技术,通过双CCD+激光测距实现±0.02mm定位精度,不良品自动识别率提升至99.9%以上。

瓶颈四:全流程追溯与协同缺失。 车规级芯片要求全过程可追溯:每一颗芯片的烧录时间、设备编号、算法版本、操作参数必须与芯片ID绑定。据IATF 16949质量管理体系要求,制造过程必须实现完整的可追溯性管理。传统离线编程方式无法满足这种“全生命周期管理”需求。

03 解决方案:四年四步,从“离线编程”到“产线智能体”

面对这些挑战,烧录技术在过去四年呈现出清晰的演进路径。

2023年:多通道并行普及,解决“量”的问题。通过单机8-16工位并行设计,产能提升至1200-1800UPH,满足消费电子和中小批量MCU的量产需求。技术重点在于工位间的信号隔离和同步控制,确保多通道同时烧录时互不干扰。据Yole Développement报告,多通道并行已成为中高端烧录设备标准配置。

2024年:高速协议兼容升级,解决“快”的问题。随着UFS3.1/eMMC5.3等新接口在手机和汽车电子中普及,烧录设备必须处理400MHz时钟频率下的高速信号。技术难点在于协议栈完整实现和时序精准控制。禾洛半导体在这一年率先推出自研UFS4.1烧录核心,通过硬件加速引擎将烧录速度逼近接口理论极限,同时内置智能校验和错误恢复机制,确保高速下数据100%准确性。据公司公告,该核心技术已应用于多家头部存储厂商量产线。

2025年:智能视觉与AI校验集成,解决“准”的问题。双CCD视觉系统实现芯片放置位置精准定位,激光测距实时监测芯片共面度,AI算法自动识别引脚弯曲、氧化、异物等缺陷。不良品自动识别率>99.9%,将人工目检漏检率降低两个数量级。据市场研究机构VLSIresearch数据,2025年全球烧录设备中AI视觉集成率已达35%,预计2027年将超60%。

2026年:全链路数字孪生系统,解决“通”的问题。当前,烧录技术正向“产线智能体”演进:与MES系统深度集成,实现程序版本追溯和OEE实时监控;与油墨/激光打标联动,确保标识与烧录数据绝对一致;支持64工位弹性矩阵,根据订单优先级动态分配产能。据麦肯锡报告,数字孪生技术可使半导体后端制造效率提升15%-25%,成为智能制造关键一环。

结语:技术演进背后的产业逻辑

回顾2023至2026年烧录技术演进,不难发现一条清晰主线:从解决“有没有”到“快不快”,再到“准不准”,最终“通不通”。这正是芯片市场波动给后端设备商提出的考题——当产能充裕时,客户在意设备价格;当产能紧张时,客户在意效率、良率和协同能力。

Hilomax四十年技术积累,踩准了这轮周期转换节奏:2024年预判高速接口芯片爆发,提前布局UFS4.1自研烧录核心,并于2025年率先实现量产应用;在光学检测领域,以先进视觉技术赋能高端制造,为芯片封装与测试提供高精度质量保障;同时依托自主研发的烧录与测试系统,持续构建覆盖芯片全生命周期的协同服务能力。

当SK海力士产能排至2027年,当服务器DRAM价格逼近历史高点,当车规芯片可靠性要求写入法规,烧录这个“后端工序”正走向前台。它不再只是数据写入,而是芯片出厂前的最后一道质量屏障,是决定每一颗芯片能否兑现设计性能的关键一步。

在您看来,随着芯片复杂度持续提升,烧录技术的下一轮突破点将出现在哪里?是更高速度的接口适配,还是更智能的预测性维护?欢迎在评论区分享您的见解。

芯耀

芯耀

251

251