新一代即插即用的数字D类音频放大器的性能远远优于传统的模拟D类放大器。更重要的是,数字D类放大器还具有低功耗、低复杂性、低噪声和低成本的优势。

电子产品生产商通常使用不带滤波器的高效率模拟D类放大器来满足手机、平板电脑、家用监控和智能音箱中便携扬声器的功率需求。这些D类放大器可直接连接到电池,以尽可能地降低损耗并减少组件数量。这些放大器还可实现大于80dB的电源抑制比,这对于避免GSM通讯的217Hz干扰来说非常重要。

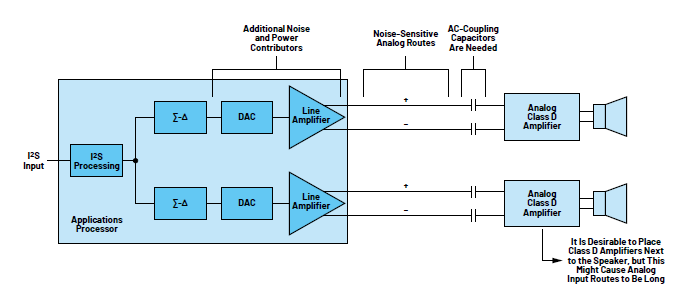

模拟D类放大器一般需要在处理器侧使用DAC和线路驱动放大器(图1),这会增加芯片成本和功耗,并导致扬声器的输出噪声。这种D类放大器还要求良好的电路板布局设计,以避免信号耦合到模拟电路而导致性能下降。

图1.使用模拟D类放大器的常规系统。处理器侧的DAC和线路驱动放大器会增加成本、功耗和扬声器输出噪声。

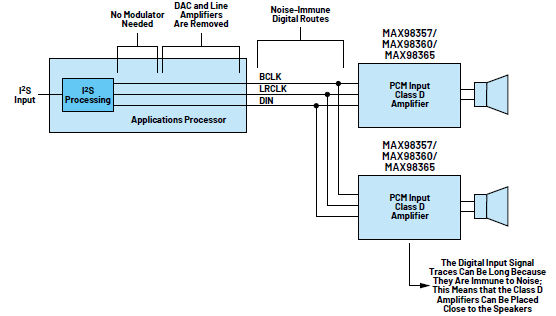

数字D类音频放大器则不需要特殊的电路板布局设计。这些单通道D类放大器可以放置在电路板上的较远位置,以最大限度地减少电池和扬声器负载之间的走线。这些放大器不需要模拟D类放大器所必需的DAC和线路驱动放大器,可以降低尺寸和成本,设计更为简单。

简化系统设计

大多数数字放大器接收脉冲编码调制(PCM)或I2S数据输入时,需要三根连接线:BCLK、LRCLK和DIN。PCM格式的输入不需要在处理器侧使用调制器或对数据进行上采样(图2)。较早的PCM输入的放大器需要干净的主时钟( MCLK)以生成无抖动的采样时钟,而较新的PCM输入的放大器,如MAX98357、MAX98360和MAX98365等,则不再需要MCLK输入,因此引脚数、功耗和电路复杂度都大大降低。

图2.PCM输入的数字D类放大器系统只需要使用三根连接线,而且处理器侧不需要调制器或对数据进行上采样。

较早的数字放大器提供可调的采样速率和/或位深度,因此在某些情况下需要对放大器进行复杂的编程。新一代的数字放大器则可以自动检测各种采样速率和位深度,支持自动配置,无需任何编程。

在多通道的实现方案中,数字D类音频放大器可以减少电路板上的外围电容和布线。PCM输入只需要BCLK、LRCLK和DIN三根连接线就可以输出立体声或8通道的TDM数据。而相比之下,模拟D类放大器一般需要两个差分输入信号共四根连接线,还需要额外的交流耦合电容(见图1和图2)。

大多数数字放大器同时需要较低的数字电源电压(1.8V)和较高的扬声器电源电压(2.5V至5.5V)。但是使用MAX98357和MAX98360等单电源供电的D类放大器可以简化电路设计并减少元件数量。MAX98365可以采用3.0V至5.5V的单电源供电,也可以采用1.8V至5.5V和3.0V至14.0V的双电源供电。数字输入的逻辑电平独立于器件的电源电压,输入逻辑电平可以是1.2V至5.5V之间的任何值,无需逻辑电平转换器。

抖动容差和时钟发生

数字D类音频放大器通常面临时钟抖动的新挑战。为了获得良好的音频质量,大部分数字输入放大器要求相当低的BCLK或MCLK的时钟抖动。数据手册通常不会具体给出抖动容差的数值,如果给出,典型值约为200ps的均方根抖动。较高的时钟抖动通常会降低放大器的动态范围或满量程THD+N性能。

在许多系统中,处理器的基准振荡器频率不是BCLK的简单倍数,因此为放大器提供低抖动的时钟并不容易。例如,13MHz是GSM电话的常见晶振频率、27MHz则通常用于视频解决方案,这些基准频率都不是44.1kSPS或48kSPS的音频采样速率的简单倍数。因此,系统通常采用复杂的小数N分频锁相环来生成音频专用的时钟。在某些情况下,该解决方案需要单独的音频基准振荡器,这会增加系统复杂性和物料成本。

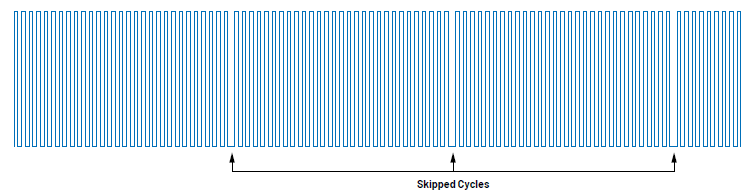

另一种更好的解决方案是使用能容忍高时钟抖动而不降低音频性能的数字放大器。这种放大器可降低系统的复杂性。在最简单的情况下,可以使用跳周期时钟来产生BCLK,但这会产生异常高的抖动。如果跳过13MHz的基准时钟周期产生6.144MHz的BCLK(48kSPS × 128OSR),则峰值抖动可达38.4ns,均方根抖动可达22.2ns(图3),这比大多数DAC所能承受的抖动还要高出两个数量级。

图3.来自于25MHz时钟跳周期生成的12.288MHz MCLK

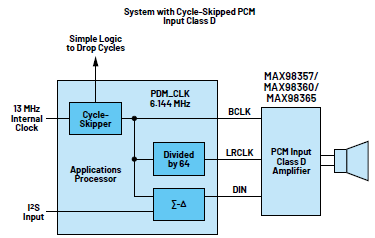

然而,新型的D类音频放大器即使在这样的时钟抖动下仍具备大于103dB的动态范围性能。跳周期时钟可通过处理器上的逻辑门电路来生成。新器件不需要锁相环解决方案必需的振荡器或环路滤波器。参见图4。

图4.小数N分频锁相环与跳周期时钟实现

图4.小数N分频锁相环与跳周期时钟实现

抖动容差测试结果

测试结果表明,使用跳周期时钟时,MAX98357、MAX98360和MAX98365的动态范围不会降低。此时,器件的动态范围性能比120dB的DAC还高出20dB。Σ-Δ型DAC抖动容差的更多详细数据可参见参考文章1。

图5.动态范围下降,跳周期时钟抖动为11.5ns rms

结语

数字无滤波D类音频放大器支持简单的电路实现,无需额外的I2C编程、MCLK输入、电平转换器和EMI滤波器,具有高效率、低EMI和高输出功率的特色。MAX98357和MAX98360采用WLP或QFN封装,输出功率可达3.2W。MAX98365采用WLP封装,输出功率可达17.6W。

参考资料

1Matt Felder, Patrick Gallagher, and Brian Donoghue. “Analyzing Audio DAC Jitter Sensitivity.” EDN Network, September, 2012.

芯耀

芯耀

698

698