RK3568是一款在性能、功能和成本之间取得了出色平衡的SoC。它或许不是性能最顶尖的芯片,但其丰富的接口、独立的NPU以及成熟的生态支持,使其成为众多工业、AIoT和多媒体应用的理想选择。我们也设计过不少RK3568 PCB的案子,设计工艺和层数是很多在我们这设计PCB的客户最关心的点。

层叠设计:8层(核心板)/6层

最小过孔设计:14/8 mil / 16/8mil

最小线宽/最小线距设计:3.5/4 mil

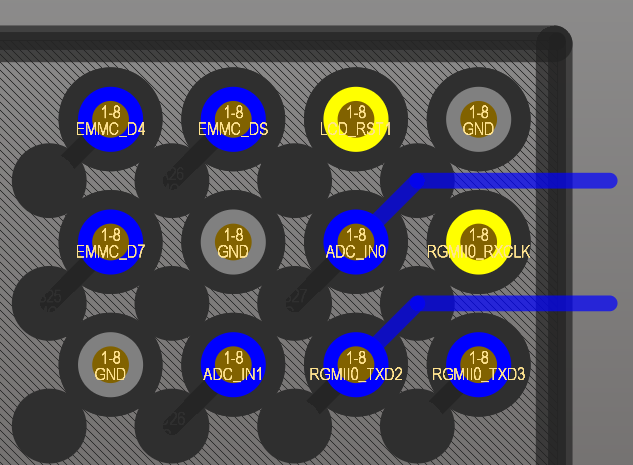

RK3568的管脚间距为0.65mm,采用常用的20/10mil的过孔已经没办法让BGA的两个孔之间穿线,这不仅会影响布线扇出,还会影响电源平面的设计;建议BGA区域采用14/8mil的过孔进行设计,这种过孔偏小,但以如今的主流PCB制板水平,已经是可以进行大批量生产且保证良率,BGA区域以外的电源可以自行根据设计情况切换换大一点的过孔;以下为使用过孔和线宽线距详解:

首先固定参数为焊盘间距 = 两个过孔中心间距 = 0.65mm = 25.591mil

1、假设采用20/10mil的过孔:

两孔边缘距离为:25.591-20=5.591mil

若只剩下5.591mil,还有过一根线,还有算上线两端与过孔的安全间距,如果按均分则得出5.591/3=1.863mil,这肯定没办法生产。

2、假设采用16/8mil的过孔:(备选)

两孔边缘距离为:25.591-16=9.591mil

若只剩下5.591mil,还有过一根线,还有算上线两端与过孔的安全间距,如果按均分则得出9.591/3=3.197mil,这个方案可以进行批量生产,但是加工难度以及生产成本会比第3种方案略高一点。

3、假设采用14/8mil的过孔:(建议)

两孔边缘距离为:25.591-14=11.591mil

现剩余11.591mil,还有过一根线,还有算上线两端与过孔的安全间距,如果按均分则得出11.591/3=3.863mil,这是可以批量生产的最小线宽和线距,但是我们可以再稍微优化一下,降低生产的难度,将线两端与过孔的安全间距升到4mil,最小线宽按3.5mil即可,计算结果如下:4+4+3.5=11.5 < 11.591mil ;这样的方案既兼顾了加工难度,也兼顾了生产成本。

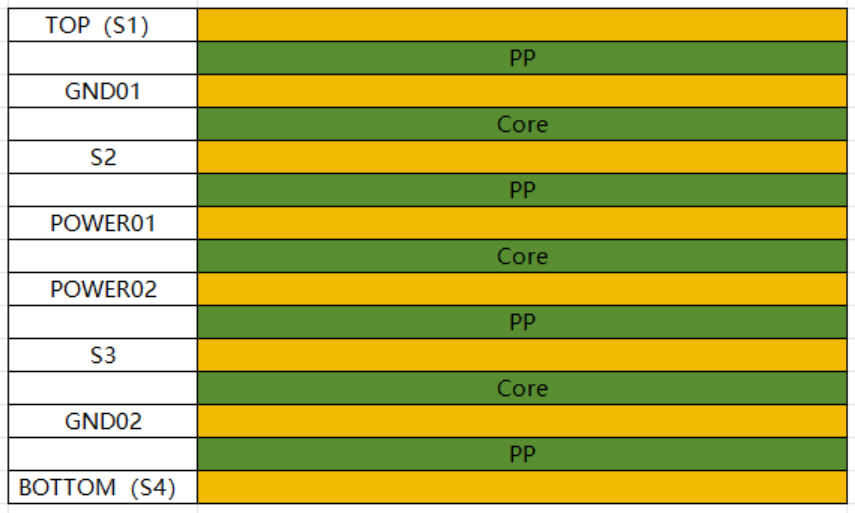

由于RK3568的电源种类和线比较多,板子空间比较大,正常情况下可以采用6层去设计,如果是密度比较高的核心板则采用8层板进行设计;核心板在层叠设计上的方案如下,此方案兼顾了无相邻信号层、层压结构对称,且具备2个电源层,能够解决电源种类多的需求;但需要注意的是:由于主电源距离GND层较远,电源平面阻抗较高,在层厚设计时,应该拉开S2与P1的间距(同理拉开S3与P2的间距),缩小G1与S2的间距(同理缩小G3与S3的间距)。

转载请注明出处:https://www.shenxs.cn

邮箱:sales@xinshengdianlu.com

作者:深鑫胜 2026.03.20

芯耀

芯耀

1157

1157