当摩尔定律逼近极限,采用2.5D/3D APT(Advanced Package Technology Platform)先进封装技术方案的Chiplet系统芯片的“More than Moore”的方式正成为芯片大厂的发力方向。

传统封装,通常是指先将圆片切割成单个芯片,再进行封装的工艺形式。例如常见的SIP、DIP、SOP等封装形式。这些封装类型都需要将芯片置于引线框中,再通过引线键合互联。在现如今人工智能ChatGPT及自动驾驶芯片等市场需求的推动下,系统需具备更高的计算能力,以能实时地处理、传输及存储大量的数据。由于此类应用所需的系统效能相当高,即使用目前最先进3nm制程所制造完成的单一芯片,也无法满足应用所需的系统效能。再者,如果是使用传统的PCB的系统集成的方式,由于PCB trace的电容及实现的物理限制,芯片之间的大量数据高速传输会产生较大的功率损耗,芯片之间的传输效能也会受到限制。因此,设计更高性能、更大规模及较低功耗的系统化芯片是必然趋势,这也使得封装技术及芯片实现技术正朝着集成化、系统化的方向发展,传统2D封装及传统意义的单芯片设计实现流程逐渐不能满足要求。

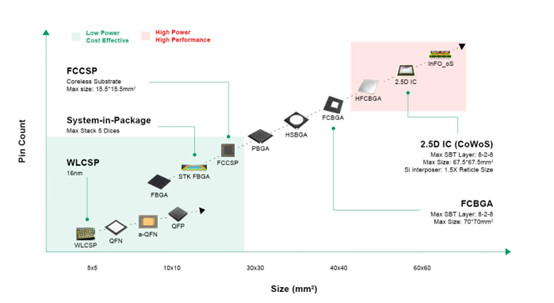

先进封装,指的是目前采用最新封装的技术,主要包括采用CoWoS、InFo、WoW等的2.5D/3D系统封装技术。由于2.5D/3D系统封装可以支持更大规模甚至不同类型芯片的集成,可以提供更高规格的设计性能,且延时时序较小,目前已经被广泛用于高性能运算、人工智能、网络通信等超大规模芯片实现制造中。由于3D系统封装及芯片设计需要设计流程周期、整体设计成本与关键技术实现,以及产品规格需求定义诸多考虑,更多厂商将目光放在了2.5D CoWoS/InFo系统芯片实现方案上。

目前,2.5D封装的代表有CoWoS/InFo技术。基于台积电(TSMC)的2.5D/3D先进制造及封装工艺,结合创意电子(GUC)自研发的GLINK D2D接口IP、 HBM3 高带宽存储接口IP,创意电子可为客户提供完善的APT技术实现方案,帮助和加速客户系统芯片Chiplet集成设计、实现及量产流程。多个客户已经基于创意电子的APT技术方案流程实现超算HPC、AI数据中心及网通芯片设计的量产。7月19-21日,2023世界半导体大会暨南京国际半导体博览会在南京国际博览中心圆满落幕。记者在现场采访到了创意电子(南京)有限公司总监肖有军,以CoWoS为例一起为大家分享先进CoWoS封装技术与创意电子的愿景。

CoWoS是啥?

CoWoS,是Chip on Wafer on Substrate的简称。这一长串名词可以分为CoW与WoS。CoW,将芯片(Chip Die)堆叠在中介层(interposer)上,WoS则是将中介层(Interposer)再堆叠在基板(Substrate)上,三层堆叠最终形成立体封装形式。这种封装形式被称为2.5D封装, CoWoS封装中的不同芯片仍旧处于同一平面之上,但在芯片(Die)与芯片(Die)之间的通信方式上由引线或基板改为了wafer,相对于传统的MCM方式,其硅片Wafer互连的延迟性能更小,功耗及性能更优。

芯片(Chip die)与中介层(Interposer)之间的通信通过硅通孔(TSV)实现。打孔,首先要在中介层硅片上涂抹光刻胶,然后进行光刻,刻蚀,沉积等步骤在硅片上制造出内部含铜的通孔,最终让芯片与基板通过通孔与基板相连接。

根据中介层材质的不同,台积电(TSMC) 的CoWoS封装技术方案可以分为三类。一种是CoWoS-S,即使用硅(Si)衬底为中介层,也是目前客户量产和使用最成熟的方案,主要是SOC和SOC、SOC和HBM存储芯片产品的集成方案使用,其布线宽度间距是0.4um。第二种是CoWoS-R,相比第一种,该技术应用重现布线层(RDL)为中介层,布线及间距是2um, 更宽的布线宽度及间距,其电源及信号完整性性能会更优。第三种是CoWoS-L,L指的是Local Silicon Interconnect and RDL Interposer,该技术实现方案支持Chip Die和Chip Die之间局部硅连接(LSI及0.4um)或者RDL布线连接, 支持所有有源芯片(Active)和无源芯片(Passive)在不同方向的集成互连。

CoWoS关键在哪?

其一是台积电(TSMC)先进工艺及封装制造技术是其关键,再有是高质量的HBM3及GLINK D2D互连界面接口IP方案,最后是完备的系统芯片Chiplet结构化集成实现方案,包括结构化DFT实现方案,支持2.5D/3D的时序收敛、后端及物理验证实现、功耗签核流程,考虑SOC Die及基板和PCB抽取RLC参数影响的电源、信号完整性、热设计签核方案等。我们重点分析后面两点因素。

(1)HBM3 /GLINK D2D接口界面互连IP方案

创意电子(GUC)表示,他们可以为超算(HPC)、人工智能(AI)、数据中心及网通等对高带宽数据应用需求的大规模芯片设计提供HBM2/HBM2E/HBM3/HBM3x高带宽界面接口IP方案,其物理界面设计针对台积电工艺做过特别功耗性能及供电设计优化,在Chiplet多芯片设计中,创意电子HBM IP可以有更宽的稳定工作电压范围。据了解,创意电子已经完成台积电16nm/12nm/7nm/6nm/5nm/3nm工艺节点的HBM 物理IP设计及流片验证, 基于台积电N3E工艺HBM3物理界面速度可以达到8.6Gbps数据传输率。与HBM 物理界面配套的HBM自研控制器IP, 支持灵活参数配置,其在随机读取模式下,带宽使用率可以达到90%以上。

创意电子设计的另外一款GLINK D2D多芯片互连界面IP。官方资料显示,它在同类业界方案中可以提供更优的高带宽、低功耗、低延迟的性能,可以为超算、人工智能、数据中心及网通芯片设计提供集成互连。在台积电2.5D CoWoS/InFo设计中,GLINK-2.5D D2D 物理IP设计每位可以提供8/16Gbps数据传输率情况下,每bit功耗仅0.25pJ/bit. 32位全双工模式下,单个物理Macro设计可以达到2/4Tbps数据传输带宽。

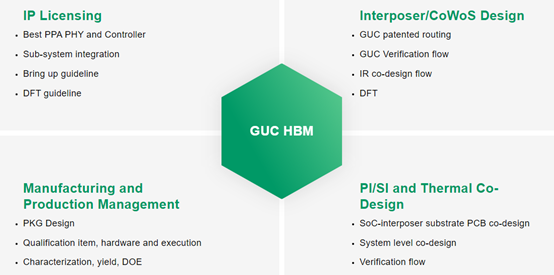

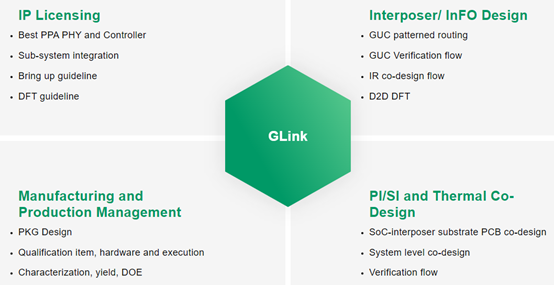

肖有军表示: “基于台积电(TSMC)的2.5D CoWoS/InFO技术实现流程,结合创意电子(GUC)的HBM和GLINK D2D互连IP方案,创意电子可以提供灵活多样的系统芯片Chiplet定制设计服务。客户既可以采购三方IP,也可以采用创意电子IP及全套Chiplet全流程方案。目前国内外均已有客户合作,并已经量产”。下面两流程图概况了创意电子HBM(图一)及GLINK D2D互连IP(图二)完整集成方案及签核服务流程。

创意电子HBM高带宽接口IP完整方案及服务流程

创意电子GLINK-2.5D/3D D2D互连IP完整方案及服务流程

(2)Chiplet集成实现及签核(signoff)

Chiplet又称为小芯片集成。该技术可以使客户通过将大型SoC设计划分为更小的模块化芯片设计,使得每个部分都能采用不同的制程工艺进行生产,通过HBM/GLINK互连IP及台积电2.5D/3D先进工艺封装技术,最后得到系统集成的Chiplet系统芯片。芯片整体上能得到更好的成本控制,更高的良率,更快的产品量产周期。

多个小芯片的集成实现,使得时序收敛、后端实现、物理验证及功耗收敛流程需要支持2.5D/3D设计,不同芯片之间OCV的设置需要考虑更多任务艺、电压及温度的组合情况,物理验证及功耗签核验证也需要考虑多芯片之间组合情况,其签核收敛流程周期会更长。

官方资料中,创意电子总经理戴尚义博士表示:“我们现已建立完备的 2.5D/3D 小芯片 IP 产品组合,可采用最小达 3 纳米的先进技术。连同我们在 CoWoS、InFO 及 SoIC 设计、封装设计、电气和热模拟、DFT 以及生产测试等领域的专业能力,我们绝对有能力为客户提供最先进的解决方案,协助客户缔造更丰硕的产品和业绩”。创意电子技术长Igor Elkanovich表示:“我们持续致力推出业界一流的晶粒对晶粒接口,以期推动小芯片革新。”

采访中,肖有军认为,人工智能ChatGPT及L4/L5自动驾驶的需求下,系统芯片设计需要处理,传输,存储更大量的数据,芯片设计规模更大及设计性能指标更高,其对CoWoS/InFO/SoIC 系统芯片Chiplet设计方案会有更多产品需求合作。客户可以依托创意电子先进封装技术实现方案(APT)及HBM/GLINK互连界面IP进行灵活定制设计服务,满足更加多元化的设计合作需求。

肖有军表示:“未来,基于创意电子与台积电的稳定合作关系,希望为客户提供更先进、更完整及更优质的芯片设计,更完备的定制化服务。对于本土客户,一次流片需要投入的资源十分庞大,创意电子希望为客户提供完备的全流程服务,为企业提供稳定的质量控制,加速客户的产品量产周期”。

来源: 与非网,作者: 刘浩然,原文链接: https://www.eefocus.com/article/1597714.html

芯耀

芯耀

2181

2181

下载ECAD模型

下载ECAD模型

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)

.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)