在英伟达CEO黄仁勋高举Blackwell架构芯片,宣布AI算力实现历史性突破的同时,很少有人注意到,这巨大成功背后隐藏着一个正在被重新定义的关键环节——先进封装。

当台积电的工程师们在2025年北美技术论坛上展示如何将12颗HBM4内存堆叠封装进单个芯片时,在场所有人都明白,半导体行业的游戏规则已经改变。

传统的摩尔定律正在逼近物理极限,单纯依靠制程微缩已无法满足AI对算力的指数级增长需求。先进封装技术,这个曾经被视为“后端工艺”的环节,如今已成为决定AI芯片性能的关键因素。

一、产业变局:从“配角”到“核心”

半导体封装的产业逻辑正在发生根本性转变。传统上,封装仅为芯片提供物理保护,如今它正直接参与性能创造。

台积电的CoWoS先进封装技术计划在2027年量产9.5倍光罩尺寸的版本,能够整合12个或更多的HBM内存堆叠到一个封装中。这种革命性的封装创新使得单颗AI芯片的算力可能达到标准处理器的40倍以上。

市场的数字更为直观:2025年,全球先进封装的销售额预计将首次超越传统封装,达到569亿美元,并有望在2028年达到786亿美元的规模。

二、技术突破:破解内存与功耗的双重枷锁

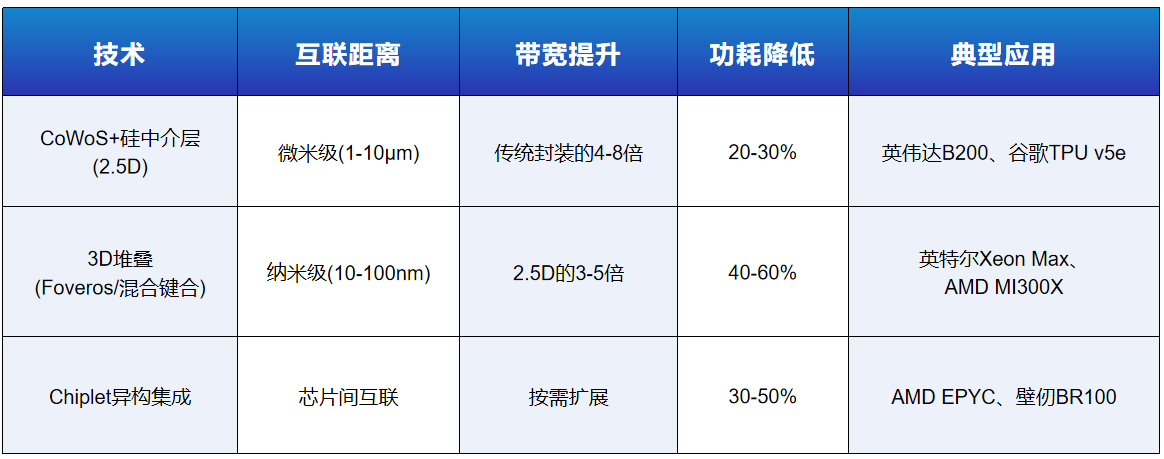

传统芯片设计中,GPU强大算力常受限于内存供给速度,形成“内存墙”瓶颈。先进封装通过硅通孔技术和混合键合技术,将HBM内存与GPU核心的互联距离从毫米级缩短至微米甚至纳米级。

台积电在2025年北美技术论坛上揭示,CoWoS技术的中介层面积最大已能做到2831平方毫米,大约是光罩尺寸极限的3.3倍。通过这种封装技术,NVIDIA B200、AMD MI300X等旗舰AI芯片能够将大型计算模块和多个HBM内存芯片高效整合。

更令人瞩目的是,先进封装技术正在创造出前所未有的巨型芯片。台积电计划推出的下一代CoWoS-L封装技术,中介层面积将扩大至4719平方毫米,甚至可以进一步拓展至7885平方毫米,相当于光罩尺寸极限的9.5倍。

三、隐形挑战:气泡问题与良率困境

随着芯片集成度不断提高,先进封装面临的核心挑战之一是制程中产生的气泡问题。这些微小的气泡可能导致芯片性能下降甚至失效,是影响封装良率的关键因素。

在复杂的三维堆叠结构中,不同材料间的界面、微凸点和混合键合区域都可能成为气泡滋生的温床。特别是在高深宽比的硅通孔填充过程中,气泡问题尤为突出。

传统的气泡去除方法在处理高密度、多层次封装结构时显得力不从心,亟需更精确、更高效的解决方案来保障制程良率。

四、中国方案:屹立芯创的技术突破

面对先进封装中的气泡挑战,中国企业正在提供创新的解决方案。南京屹立芯创半导体科技有限公司凭借其热流与气压核心技术,推出了专门针对先进封装制程的除泡与压膜解决方案。

屹立芯创自主研发的全自动型晶圆级真空贴压膜系统WVLA,采用有别于传统滚轮式贴膜机的创新技术。其独特的真空下贴压膜和软垫气囊式压合专利技术,有效解决了预贴膜在真空压膜过程中产生气泡的问题。

这套系统已实现国产定制化量产,兼容8英寸及12英寸晶圆尺寸,特别适用于表面凹凸起伏的晶圆,可实现业内领先的高深宽比填覆效果。

屹立芯创的除泡系统则专注于解决半导体先进封装中的气泡问题。依托热流和气压两大核心技术专利,公司打造了全系多种功能客制化智能机台,提供底部填胶、环氧树脂灌封、芯片贴合、OCA贴合等多种制程工艺中的气泡整体解决方案。

五、时代已至:封装定义算力的产业新规

硅片之上,是晶体管编织的算力梦想;封装之中,是无数微小连接创造的性能奇迹。当摩尔定律放缓脚步,先进封装正成为AI芯片突破算力瓶颈的新引擎。而在这场全球性的技术竞赛中,中国力量正以创新的解决方案,为芯片制造的关键环节贡献着不可或缺的智慧与工艺。

芯耀

芯耀

1166

1166