常见的振荡现象:

开关瞬态振荡:漏源/集电极振荡:在开关过程中,漏源电压 Vds 或电流 Ids 波形上出现严重振铃。

最危险的振荡:Vds 和 Ids 的交叉振荡。在硬开关关断时,Vds 上升和 Ids 下降的过程中产生的剧烈振荡,可能导致电压尖峰超过器件额定值,引发失效。

栅极振荡:在开通和关断瞬间,栅源电压 Vgs 波形上出现高频衰减振荡。

桥臂串扰:由于高速开关引起的 dv/dt 和 di/dt 通过寄生电容耦合,导致同一桥臂中关断器件的栅极产生虚假电压脉冲,可能引起误开通(米勒效应)。

SiC 牵引逆变器模块 并联驱动振荡的抑制方法:

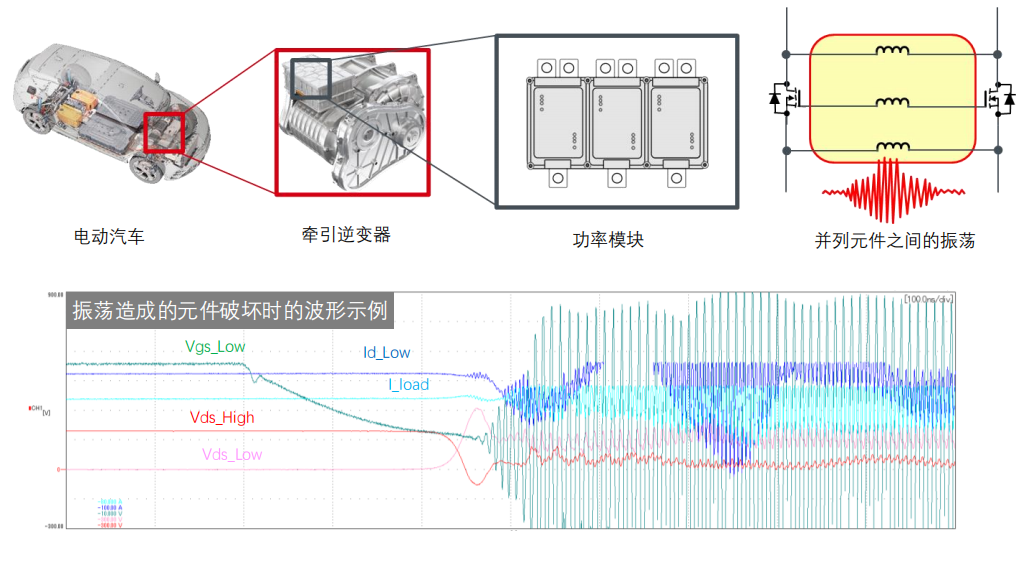

SiC MOSFET 与传统 Si 器件相比,具有高电压、大电流、高速驱动、低损耗、高温稳定等诸多优点,是新一代器件。 近年来,利用这些优异特性,作为向大功率发展的电动汽车 (EV) 的牵引逆变器电路,并联连接多个 SiC MOSFET 元件的功率模块被使用的情况越来越多。

另一方面,由于并联使用这样的高速元件,有时会发生元件间的并联驱动振荡 (以下简称振荡)。发生振荡的话元件有破坏的危险,因此抑制对策是市场的重要课题之一。

本应用笔记将介绍有效抑制功率模块振荡的方法。

1、基础理论

1-1. 振荡发生的机制

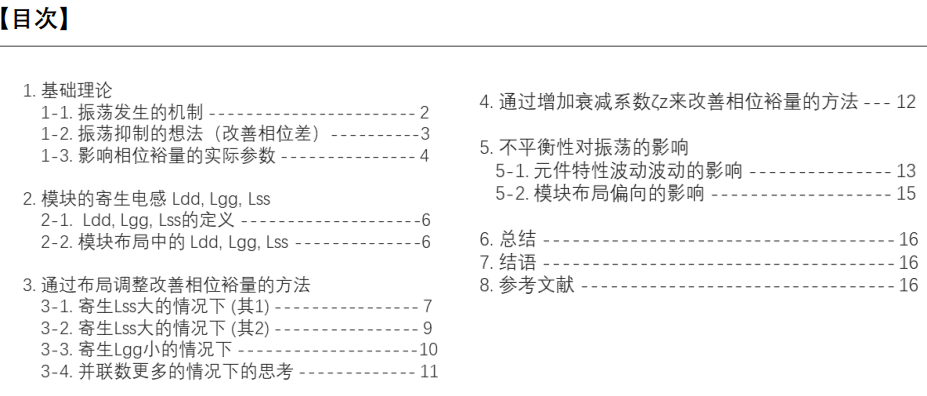

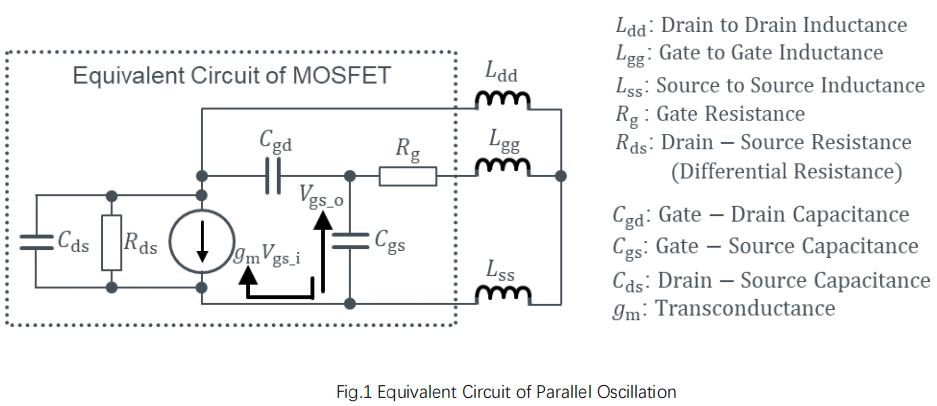

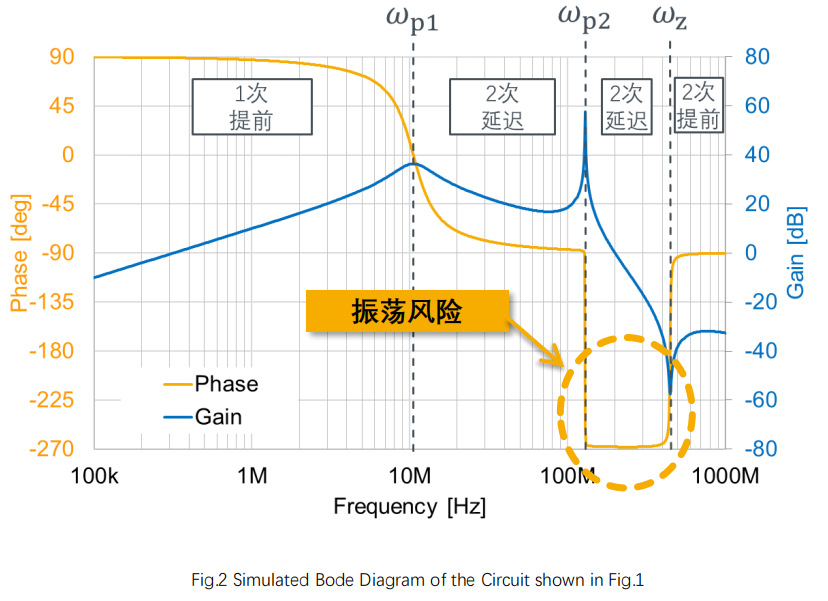

并联开关设备的稳定性分析可以使用 Fig.1 所示的等效电路进行评估 [1]。这里,Ldd, Lgg, Lss是含有互电感的寄生电感成分[2]。另外,Rds成为开关瞬态时的微分电阻。关于这个,使用 PLECS®查询 Vgs_i到 Vgs_o的开环特性的话,可以得到 Fig.2 那样的 Bode 曲线图。从 Fig.2 可以看出,ωp2和ωz相距较远,因此两者之间的相位小于-180o。根据奈奎斯特的稳定判别法,Gain 在 0dB 的时候相位在-180°以下的话有可能会发生振荡,这成为并联模块的振荡风险。

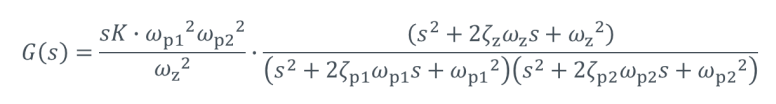

Fig.2 中的 Bode 图可以根据 、ωp1, ωp2, ωz 的各个极点和零点,从低频侧依次划分为一阶提前区、二阶延迟区、二阶延迟区和二阶提前区。 因此,这个系统中的一轮传递函数 G(s) 可以用以下的公式来表达。

Fig.2 中的 Bode 图可以根据 、ωp1, ωp2, ωz的各个极点和零点,从低频侧依次划分为一阶提前区、二阶延迟区、二阶延迟区和二阶提前区。 因此,这个系统中的一轮传递函数 G(s) 可以用以下的公式来表达。

1-2. 振荡抑制的想法(改善相位差)

为了抑制振荡,“增加相位余度,降低增益”就可以了。但是在并联模块的情况下,由于降低增益非常困难,作为根本对策“增加相位余量度”是最有效的。

Fig.3 解释了难以降低增益的原因:在二阶延迟系统中,当 ζp2的值小于 1⁄√2 时,会出现增益峰值,其大小由 ζp2的值决定(ζp2越小,增益峰值越陡、越大)。 此外,如 1-1 所述,ζp2中包含的 Rds是开关瞬态期间的差分电阻,因此具有数 kΩ 的较大值。由于 Rds较大,ζp2与 1⁄√2 相比非常小,因此增益峰值非常大。 如上所述,由于增益峰值较大,很难降低增益,因此 "增大相位裕量 "是抑制振荡的有效方法

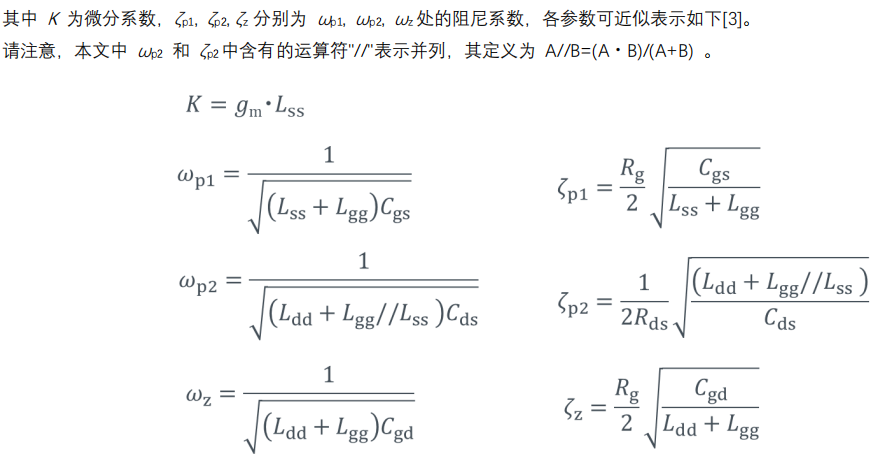

那么,怎样才能增加相位裕量呢? 正如 1-1 所说明的,ωp2 和 ωz 的距离分开的话相位会低于-180°。换句话说,如果把ωp2 和ωz 靠近的话,可以使相位裕量变大。一般的并列模块 ωp2<ωz 且 ωp2/ωz<1,因此“使ωp2 和 ωz 接近,以增大相位裕量”也就是“使ωp2/ωz比增大,以接近 1”。

Fig.4 显示根据 ωp2/ωz比的变化,相位特性变化的情况。如 Fig.4 所示,ωp2/ωz比越大,相位裕量就越大,振荡抑制就变得可能。另外,ωp2/ωz≧1 时,理论上不会产生振荡。

振荡的根本对策: 增加相位裕量(增大ωp2/ωz 比)

1-3. 影响相位裕量的实际参数

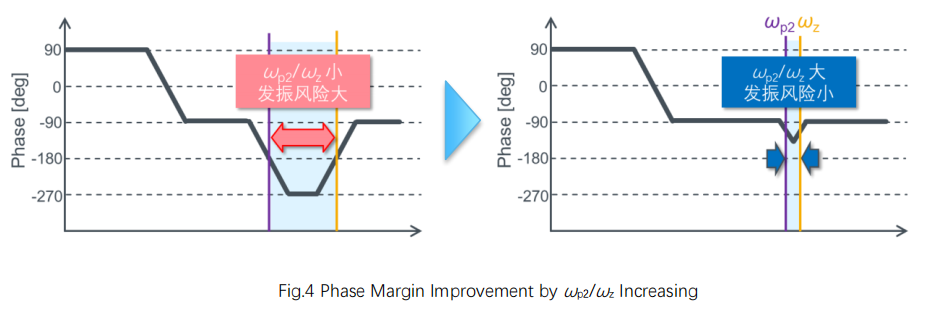

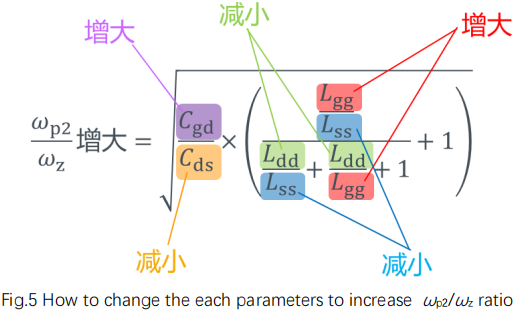

在 1-2 中,ωp2和ωz的偏离程度 (ωp2/ωz比) 对相位余量度有很大影响。那么,为了改变ωp2/ωz比,具体应该改变哪个参数呢?本章将详细解说影响ωp2/ωz比的实际参数。正如 1-1 所说明的,ωp2 和 ωz分别可以用以下的公式来表达。

根据这些计算 ωp2/ωz比,可以得到以下关系式。

根据前页ωp2/ωz 比的关系式可知,为了增大ωp2/ωz 比以增加相位裕量,只要将各参数设置为 Fig.5 所示的“Cgd 和 Lgg 大,Cds とLss和 Ldd小”即可。

但是,在实际的模块中 Ldd的 ωp2/ωz比的影响和其他参数相比是非常小的。因此,为了增加相位裕量,调整 Ldd以外的参数的方法是有效的。

提高相位裕量: Cgd和 Lgg大,Cds 和 Lss 小。

另外,Cgd 和 Cds 是寄生在 MOSFET 元件上的容量成分,所以现实上很难改变。因此,抑制振荡对策中最重要的是 Lgg 和 Lss 的设计,也就是“模块布局设计”。

抑制振荡的对策中最重要的是“布局设计”

另外,从相位裕量增加的观点来看,Cgd越大越好,不过,Cgd越大,作为其互斥事件,开关损耗的增大和 Self Turn-on 的风险也变大,所以平衡好的设计变得困难了。

2、模块的寄生电感 Ldd, Lgg, Lss

2-1. Ldd, Lgg, Lss 的定义

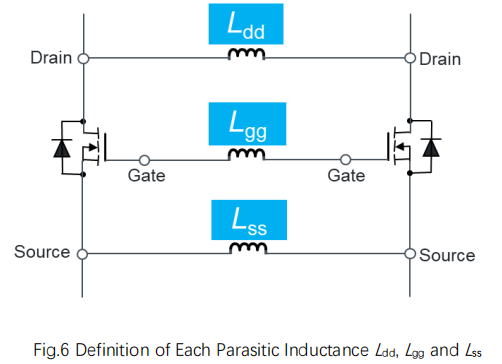

在 Fig.6 中,表示模块中影响相位裕量 (ωp2/ωz比) 的各寄生电感 (Ldd, Lgg, Lss) 的定义。用一句话来概述,Ldd, Lgg, Lss 是并联连接的元件的各端子之间存在的寄生电感。另外,Fig.1 是从中点看时的一侧,所以 Fig.1 中的 Ldd, Lgg, Lss 各值是 Fig.6 的一半。使用 Fig.1进行稳定性分析时,请注意这一点。

2-2. 模块布局中的 Ldd, Lgg, Lss

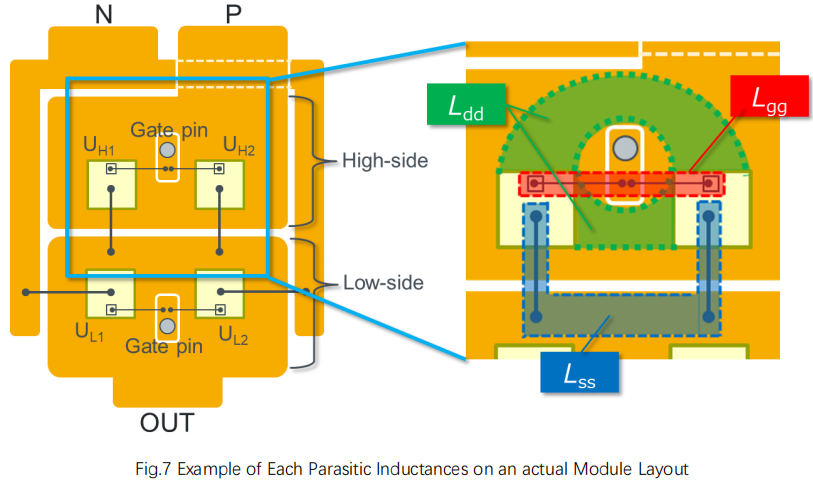

本节以 Fig.7 的模块布局为例,说明布局的哪个部分相当于上述 Fig.6 的 Ldd, Lgg, Lss 。这里以高边为例进行说明,低边的方式也是一样的。图中连接各元件的黑线表示接合线。另外,为了简单易懂的说明,省略了栅极驱动布线的负侧 (以后的布局图也一样)。

Fig.7 右侧的图中,Lgg用红色表示,Lss用蓝色表示,Ldd用绿色表示的部分,相当于各寄生电感。Lgg几乎和导线的寄生电感相等。Lss是连接元件的各导线,以及连接它们的铜箔部的合成电感,Ldd是绕过栅极引脚的上旋和下旋两路合成电感。

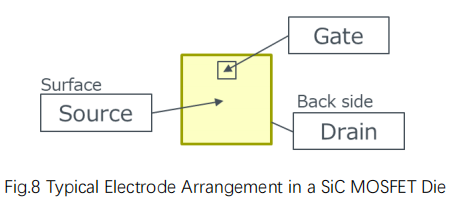

SiC MOSFET 元件中,一般的各电极 (Gate, Drain, Source) 的配置如 Fig.8 所示。

3、通过布局调整改善相位裕量的方法

在本章的 3-1 到 3-3 中,为了让读者更容易理解布局设计的要点,以某模块布局为例,以“发生振荡⇒布局问题点梳理⇒修正”为例进行说明。在实际的布局设计时,根据本章的内容 (哪里不好?为什么不好?如何修正才好?) 请在充分理解的基础上,设计注意不要产生振荡。

正如第 1-3 节所述,为了抑制振荡,本章将要介绍的“布局设计”是最重要的内容。在第 4 章也会说明追加 Rg_add 来改善相位裕量的方法,但是因为需要额外的成本和安装空间,所以请把它作为布局设计的辅助来考虑。另外,如果没有充分实施第 3 章和第 4 章的相位裕量的对策,只实施第 5 章所说明的“调整特性偏差”的对策,也不能成为充分的振荡对策。因此,作为振荡对策的重要度是以下的顺序。

振荡对策的重要度:3 章 > 4 章 > 5 章

3-1. 寄生 Lss 大的情况下 (其 1)

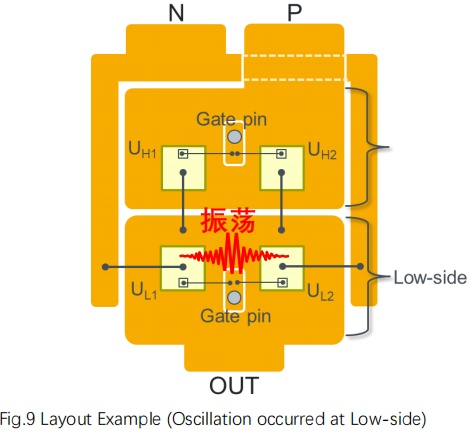

在 Fig.9 这样的模块布局中,假设“低边 MOSFET UL1 - UL2之间发生振荡”。

正如在 1-3 中说明的那样,模块的寄生电感对相位裕量有很大影响,所以要按顺序确认 Fig.9 的寄生电感中是否包含使低边相位裕量下降的振荡因素。

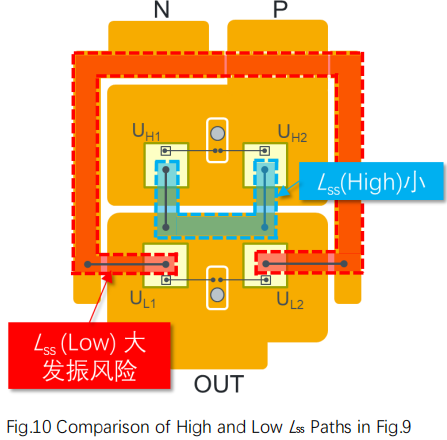

注意 Lss (参照 Fig.10),高边的路径 (蓝色) 很短,低边的路径 (红色) 由于经过 N 引脚绕了很多圈,所以非常长。因为通常路径越长寄生电感越大,在这个模块低边的 Lss 非常大。正如在 1-3 中说明的那样,Lss 越大,相位裕量就越低,所以可以认为这是振荡因素。

再者,因为 Lgg的高边和低边没有差,这个情况下,Lgg成为振荡因素的可能性低。

为了抑制这个振荡,只要降低低边的 Lss 就可以了。一般来说,有以下三种方法可以降低寄生电感。你可以使用以下方法中的任何一种。请在考虑布局和其他限制的基础上选择合适的方法。

减小寄生电感: ①增加并联路径 ②缩短路径 ③增加路径截面

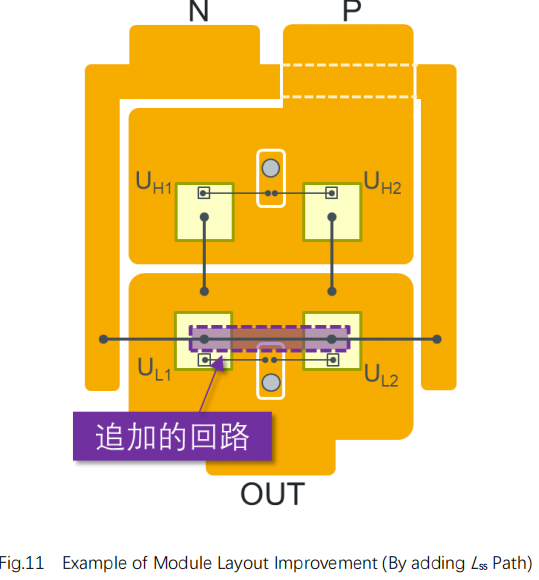

这里使用“①增加并联路径”和“②缩短路径”的方法。修改后的布局如图 Fig.11 所示。在 Fig.11 中,相对于原来的模块布局 (Fig.9),追加直接连接元件 UL1和 UL2的 Source 引脚的线。这样做的话,在经过原来 N 引脚的绕圈路径的基础上追加关联路径的同时,路径长度也能缩短,因此低边的 Lss大幅降低。根据这个 Lss降低,相位裕量提高振荡被抑制。

另外,这里假设的是低边发生振荡的情况,但根据布局设计的不同,当然也有的高边发生振荡的情况(关于这个例子,将在下面的3-2 中进行介绍)。另外,在 Fig.11 中,用线形成了追加路径,但也可以使用线以外的 (Ribbon、Clip、Busbar 等)东西。

3-2. 寄生 Lss 大的情况下 (其 2)

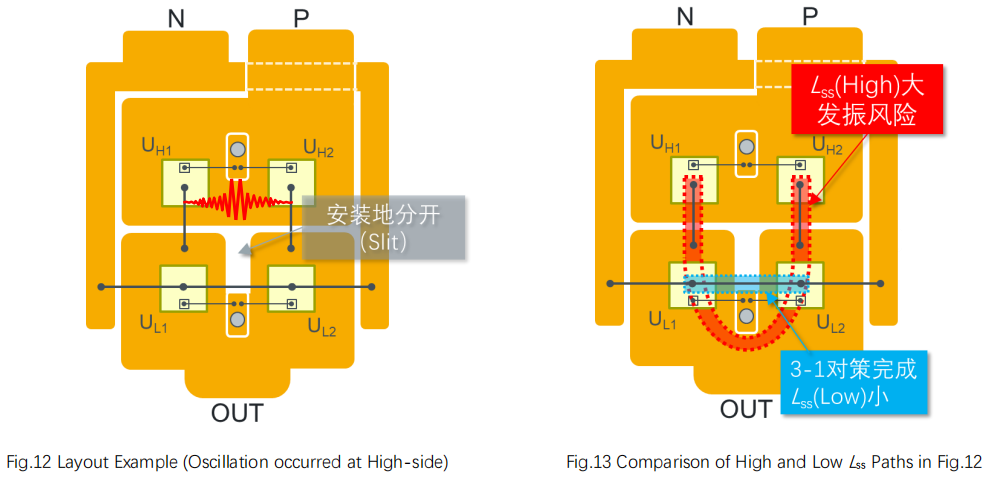

在像 Fig.12 这样的模块布局中,假设“高边的 MOSFET UH1–UH2之间发生振荡”。作为 Fig.12 的布局的特征,低边的安装地的一部分有切断 (缝隙) 的点。另外,低边的 Lss已经实施了与 3-1 相同的对策 (添加路径)。

与 3-1 一样, 确认 Fig.12 的寄生电感中是否包含使高边的相位裕量降低的振荡因素。

注意 Lss (参见 Fig.13),低边是较小的 Lss,因为它和 3-1 的对策相同 (追加的并联路径:蓝色)。另一方面,高边的路径,由于安装地的切断,OUT 引脚侧需要大绕圈,所以 Lss变大。因此,这个 Lss大的点被认为是振荡因素。另外,Lgg在高边和低边方面没有差,这种情况下,Lgg成为振荡因素的可能性很低。

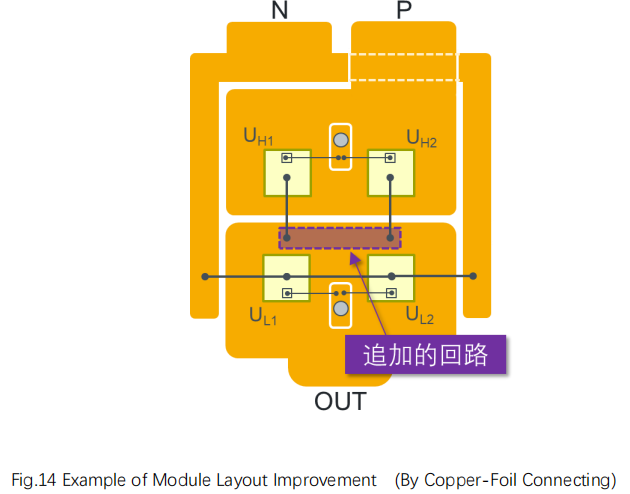

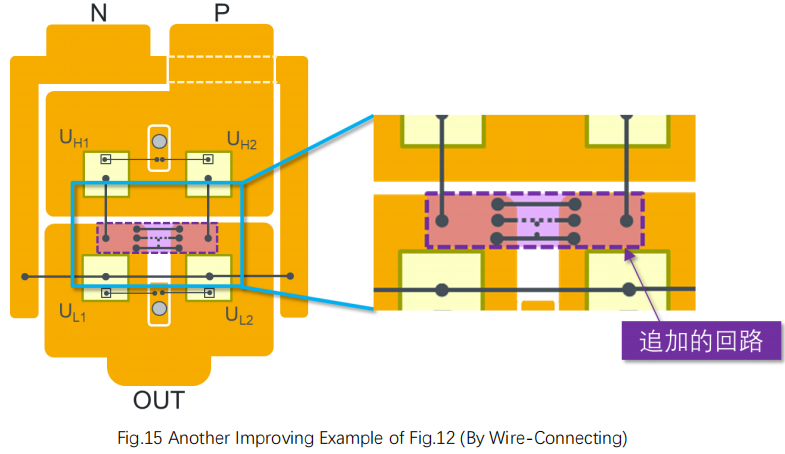

为了抑制这个振荡,只要降低高边的 Lss就可以了。这里和 3-1 一样,使用“①增加并联路径”和“②缩短路径”的方法。修改后的布局如 Fig.14 所示。在 Fig.14 中,用铜箔连接了原来的模块布局 (Fig.12) 的狭缝,增加了新的路径。通过这样做,在经过原来的 OUT引脚的大绕圈路径的基础上追加并联路径的同时,路径长度也能缩短,因此高边的 Lss大幅降低。根据这个 Lss降低,相位裕量提高振荡被抑制。

【补充】

Fig.14 用铜箔添加了路径,也可以像 Fig.15 那样用线连接。但是,由于引线与铜箔相比寄生电感较大,所以像这种以降低电感为目的的情况下,像 Fig.15 那样并联多条引线比较理想。线数量少的情况下,可能不能达到与 Fig.14 同等的 Lss降低效果。像这样,根据目的适当调整线数和使用部件等,就可以不易产生振荡的布局设计。

3-3. 寄生 Lgg小的情况下

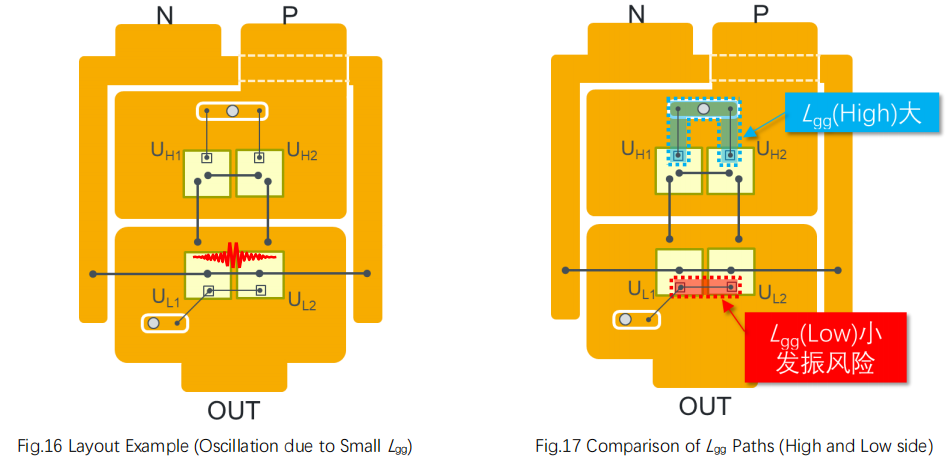

本节对寄生 Lgg小的情况进行说明。在 Fig.16 这样的模块布局中,假设“低边 MOSFET UL1-UL2之间发生振荡”。与 3-1、3-2 一样,确认 Fig.16 模块的寄生电感中是否包含导致低边相位裕量下降的振荡因素。关注 Lgg (参照 Fig.17),由于低边的 Lgg (红色) 是所谓的“串珠连接”,所以与高边 (蓝色) 相比寄生电感非常低。正如在 1-3 中说明的那样,Lgg越小相位裕量就越低,所以可以认为这是振荡因素。

另外关于 Lss,由于高边和低边都以最短路径连接,寄生电感非常小,Lss成为振荡因素的可能性很低。

为了抑制这个振荡,增加低边的 Lgg就好了。为了增加寄生电感,以下 3 种方法是有效的 (如果进行与 3-1 介绍的“减少寄生电感”相反的对策,电感就会变大)。

增加寄生电感: ①减少并联路径 ②延长路径 ③减少路径的截面

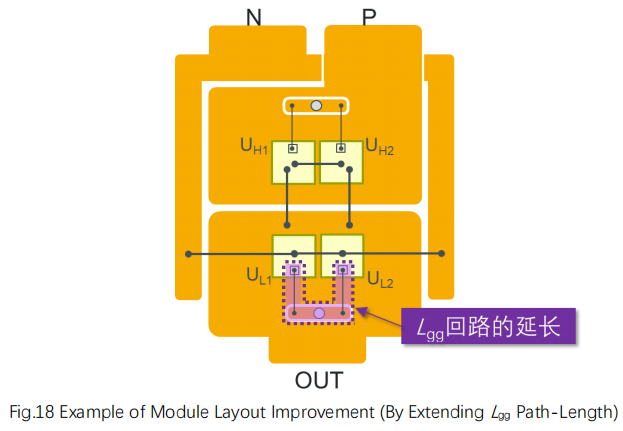

这里采用“②延长路径”的方法,在 Fig.18 中展示其改善布局。在 Fig.18 中将低边的 Gate 驱动布线,从 Fig.17 的“串珠连接”修改为与高边相同的“来自 Gate 引脚的均等布线”,延长路径 (增加 Lgg)。根据这个,相位裕量增加振荡被抑制。

另外,Fig.18 的改善布局不仅仅是增大 Lgg,在使并联元件之间的开关速度一致这一点上也对抑制振荡有效 (详细参照 5-2)。

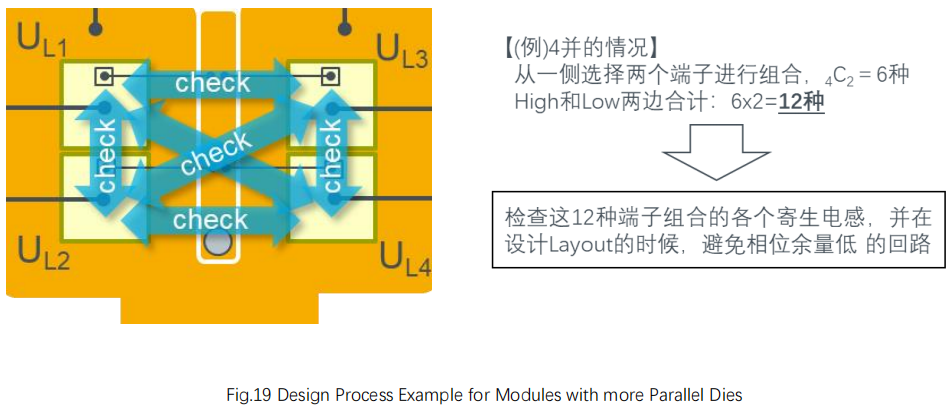

3-4. 并联数更多的情况下的思考

在 3-1 ~ 3-3 中,在 2 个并联模块中,从 2 个元件间的各寄生电感中筛选出对相位裕量产生不良影响的成分,修正了其布局。虽然实际模块的并联数量更多(一般为 4 ~ 8 个并联),但其基本布局设计方法与 2 个并联的相同。也就是说,请按顺序确认各元件的组合寄生电感,设计不要使特定元件之间的相位裕量恶化 (参照 Fig.19)。请注意,即使元件间只有一处相位裕量低的路径存在的话,都有发生振荡的危险。

4、通过增加衰减系数 𝜻𝒛来改善相位裕量的方法

第 3 章关注寄生电感 (模块布局),介绍了改善相位裕量方法,这个相位裕量也可以用调整零点的衰减系数ζz的方法来改善。本章将具体说明方法。

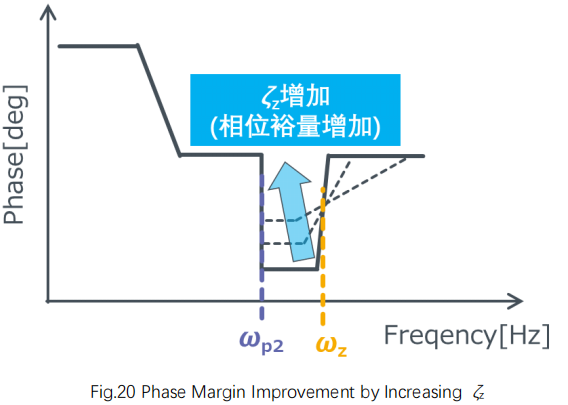

如 Fig.20 所示,即使ζz变大,ωz的值本身也不会变化,但是由于在零点处的相位特性的斜率变缓,所以可以改善相位裕量。

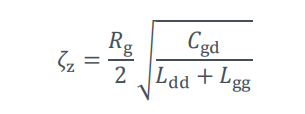

具体说明增大ζz的方法。正如 1-1 所述,零点的衰减系数ζz可以用以下的公式来表现。

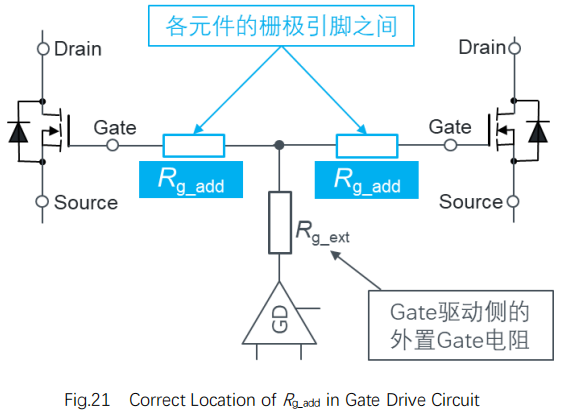

由上式可知,如果 Rg变大的话ζz就能变大。这里的 Rg是指 Fig.21 中的 Rg_add。请注意栅极驱动电路中 Rg_add的位置。Rg_add如果不像 Fig.21 那样,在并联连接的各元件的栅极引脚之间配置,就不能得到相位裕量的改善效果。另外,单纯地追加 Rg_add的话会增大交换损耗,所以在追加 Rg_add的时候,为了不对开关损耗产生不良影响,最好同时调整 Rg_ext。

另外,追加 Rg_add的方法也伴随着缺点 (需要额外的成本和安装空间),所以请将其作为第 3 章布局设计的辅助。并且,希望 Rg_add的

电阻值偏差尽可能小。如果电阻值偏差大的话,开关速度偏差会导致振荡恶化,所以请尽量使用精度好的电阻 (理由参照 5-1)。

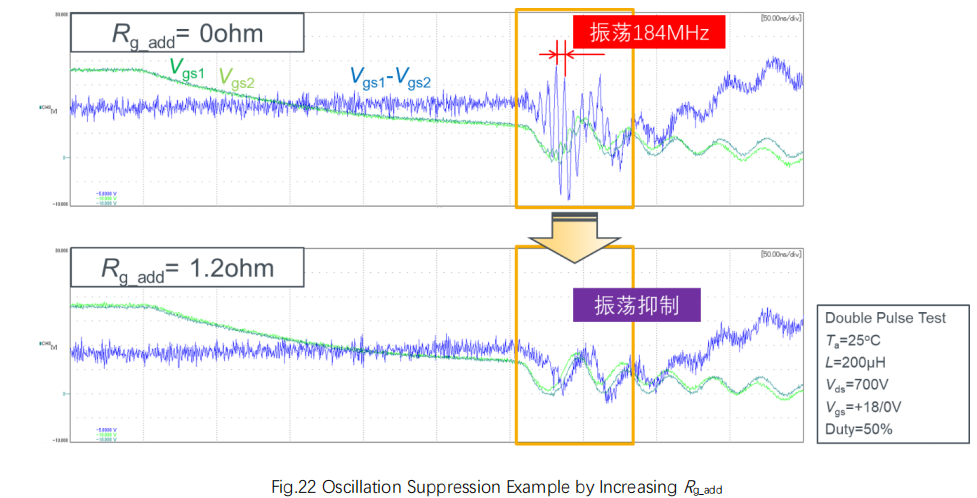

在 Fig.22 中示出根据 Rg_add的振荡改善的示例。在两个并联模块的双脉冲测试中,针对 Rg_add=0ohm 和 1.2ohm 的情况,对比了Vgs的 Turn-off 波形。为使开关速度相同,Rg_ext 已分别进行调整。由于 Vgs的振荡波形非常微小,所以通过显示各元件的 Vgs差分波形 (Vgs1-Vgs2 :蓝色) 来方便理解。

在 Rg_add =0ohm 的情况下,从平台区间的末端附近可以看到 184MHz 的振荡波形,但是只要在 Rg_add上追加 1.2ohm 就可以完全抑制振荡。

5、不平衡性对振荡的影响

5-1. 元件特性波动波动的影响

在 Fig.23 中,表示元件的栅极阈值电压 Vth的波动 (⊿Vth) 和振荡强度的评估结果。评估使用的模块是两个并联模块。⊿Vth=207mV (Vth波动中等) 时的振荡振幅为 7.3V,⊿Vth=396mV ( Vth波动大)时增加到 10.8V。也就是说,“⊿Vth越大振荡越恶化”。

为什么⊿Vth大的话振荡会恶化呢?一般来说,振荡是在不稳定的状态下加上“干扰”才会发生的 (单纯的不稳定状态是不会发生振荡的。振荡的发生需要某种触发因素)。而且,这种干扰越大,振荡就越恶化。在 Fig.23 的例子中,Vth 波动 (⊿Vth)引起并联连接元件间的开关动作波动,该波动成为干扰,因此可以认为振荡恶化。

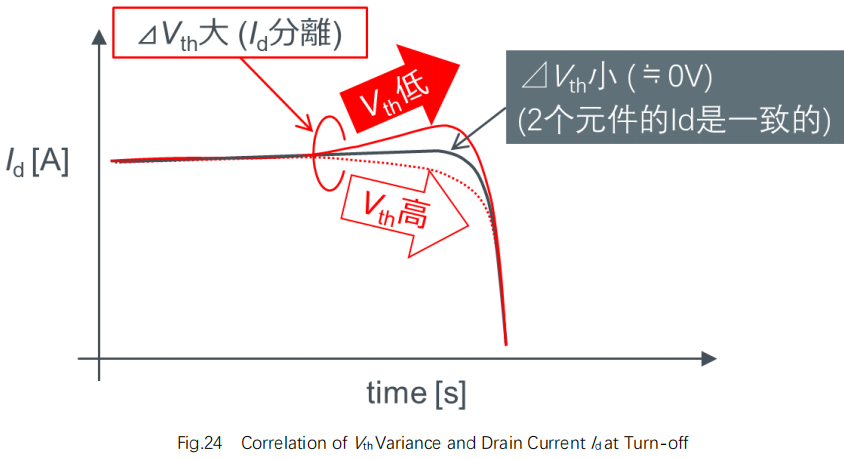

关于干扰,进一步详细说明。Fig.24 是显示在两个并联模块的 Turn-off 时,不同 Vth的漏极电流 Id的工作图形。⊿Vth小的情况下(≒0V) の Id波形用黑线表示,这种情况下各元件的 Id波形一致。⊿Vth大的话各元件的 Id 按照 Turn-off 分成 2 个。具体来说,Vth低的Id 向上移动 (红实线),Vth 高的 Id 向下移动 (红虚线)。这是因为 Vth 的高低不同,Turn-off 速度也不同 (Vth 高:Turn-off 快,Vth 低: Turn-off 慢)。

以下总结了影响 SW 速度和 Id的元件特性。为了不使振荡恶化,关于封装的元件,尽可能备齐这些特性的事重要。

影响 SW 速度和 Id 的元件特性:Vth、Qg、寄生容量( Cgs, Cgd, Cds )、Ron、内置二极管、内部 Rg

【补充】为了不使振荡恶化,元件特性的波动越小越好,不过,请注意不是“抑制特性波动就能抑制振荡”的意思。在 1-2 中已经说明过,振荡的根本对策是“提高相位裕量”。即使不充分实施相位裕量的对策只减小特性波动,振荡的抑制也是困难的。

5-2. 模块布局偏向的影响

正如在 5-1 中所述,由于干扰元件之间的开关 (SW) 速度和 Id波动的话振荡会恶化。同样,模块布局的“偏向”也会在这 2 点 (SW速度和 Id) 上产生波动,可能会导致振荡恶化。

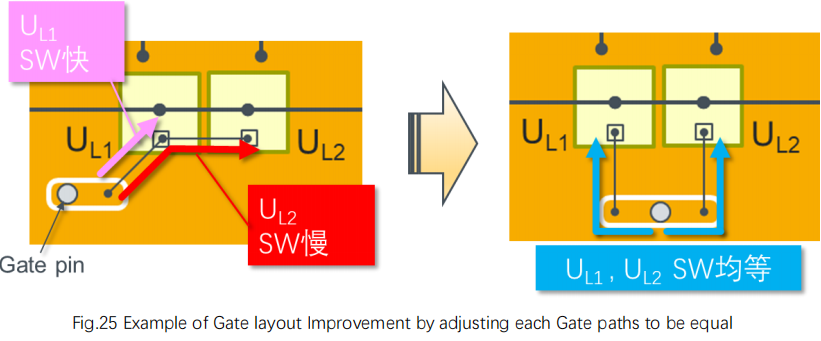

例如,在 Fig.16 的低边介绍的将线串珠连接的 Gate 驱动布局中,元件 UL1和 UL2之间的 SW 速度会产生波动,因此有振荡恶化的危险。为了防止 SW 速度波动引起的振荡恶化,最好修改 Fig.25 右侧的布局 (在 3-3 中修改布局的目的是为了增加 Lgg,即使是为了 SW 速度均等,Fig.25 的修正是有效的)。

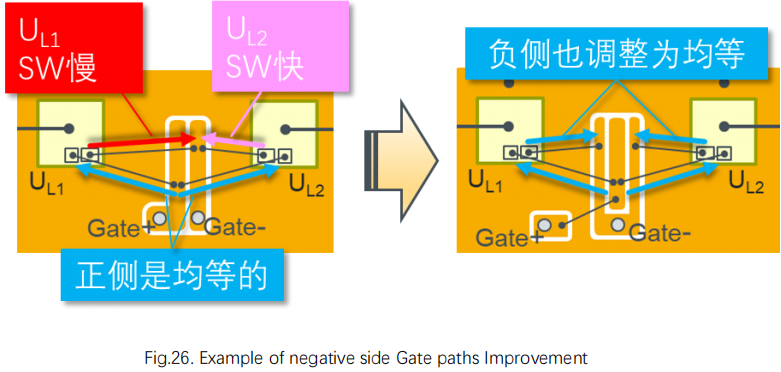

另外,目前所有的图中,为了简单地说明 Gate 驱动配线负的部分省略了,不过,关于负的部分也和正的部分一样应该考虑。例如,在 Fig.26 左侧的布局中,正的部分是均等的,但负的部分有偏差,因此 UL1 和 UL2 之间的 SW 速度会产生波动。这种情况下,像 Fig.26 的右侧那样,为了使负的部分也均等修改布局比较好。

6、总结

为了抑制振荡,只要“增加相位裕量,降低增益”就可以了。但是,作为根本对策,“增加相位裕量”是最有效的 (因为ωp2会产生2 次延迟的增益峰值,很难降低增益)。

衡量“相位裕量”的指标是“ωp2/ωz比”。ωp2/ωz比越大,相位裕量越大,越稳定。

为了增加 ωp2/ωz比来提高相位裕量,“Cgd和 Lgg大,Cds和 Lss相反小”就可以了。

Cgd 和 Cds是元件的寄生电容,所以很难从后面进行调整。因此,为了增加相位裕量,适当地设计模块的各寄生电感 (即布局)是重要的。

为了合理设计模块布局,需要逐一确认各元件之间的寄生电感,同时调整整体平衡,使特定元件之间的相位裕量不降低。这是抑制振荡最有效的方法。

除了布局调整以外,作为增加相位裕量的方法,还有追加 Rg_add以增大零点的衰减系数ζz的方法。但是,如果追加 Rg_add

则需要多余的部件成本和安装空间,因此最好将其视为对上述布局设计的辅助。

如果元件之间的特性不一致,则由于干扰变大,振荡恶化。因此,希望特性波动小。但是如上所述,振荡的根本对策是“增加相位裕量”。如果不充分实施相位裕度措施,即使只减少特性变化,也很难抑制振荡。

模块布局的偏向,也有可能造成较大的干扰,导致振荡恶化,所以在实施布局设计时,也要注意这一点。

7、结语

正如本篇所述,为了抑制模块的振荡,“布局设计”是最重要的。如果您对布局设计有什么不明白或困扰的地方,请随时向我司的营业窗口咨询。除了本篇中介绍的方法和振荡对策外,我们还拥有更先进的分析方法和振荡对策方面的丰富技术知识,相信能帮助客户解决问题。

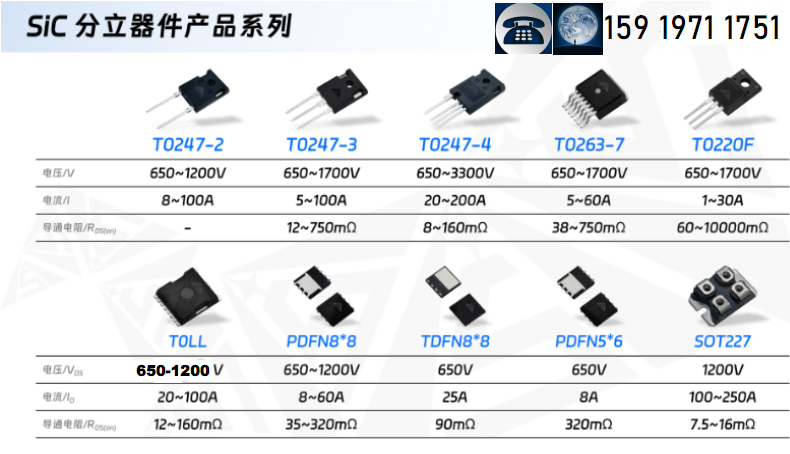

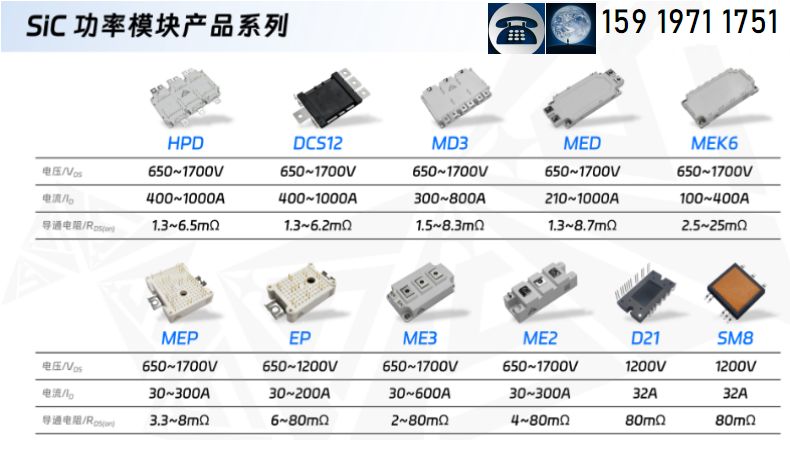

碳化硅模块与碳化硅MOSFETs产品概览

芯耀

芯耀

9722

9722