引言:在现代芯片制造工艺中,光刻是非常重要的一个步骤,其过程采用类似照相机的原理,光刻机发出的光通过具有图形的掩模版在晶圆上进行曝光成像,从而实现将电路图转印到晶圆上。在理想情况下,晶圆上的成像图形会与掩模版上的布局设计完全一样。但是,当掩模版图形的关键尺寸小于曝光波长的时候,由于衍射效应晶圆上的成像会失真,从而与掩模版的布局图形不是很吻合,此时就需要计算光刻OPC(Optical Proximity Correction)技术对掩模版的图形进行修正,从而保证印在晶圆上的图形符合最初的设计。

东方晶源从创立之初便聚焦计算光刻领域,推出PanGen平台。经过近十年的发展PanGen已经成为集合精确的制程仿真、DRC、SBAR、OPC、LRC、DPT及SMO等完整功能链条的平台。同时,通过丰富、大量的产线应用,东方晶源已经成为国内计算光刻领域的开拓者、领导者。近期,结合产业应用及发展痛点,东方晶源推出两款新产品PanGen DMC和PanGen dFO,本文将对这两款产品的研发背景、应用及成果进行详细介绍。

PanGen DMC——基于快速工艺反馈,提供更全面的可制造性检查

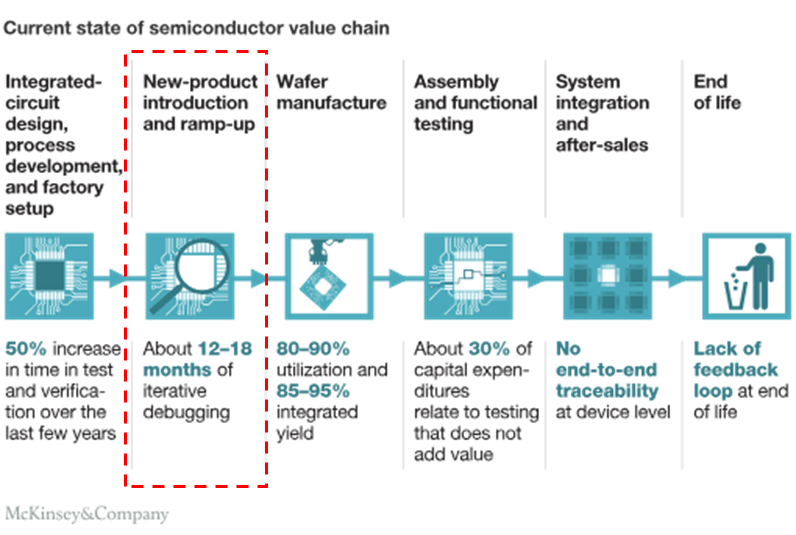

随着技术节点的演进,工艺本身变得越来越复杂,Designer愈发难以对工艺有全面、系统的认识,导致新产品在工艺端流片时需要反复迭代,经历更长时间的Yield Ramping,增加了芯片投产的成本,也延长了产品面市的时间。据麦肯锡统计,目前半导体行业内新产品从导入流片到最终良率(Yield)ramp up,大概需要12 ~ 18个月反复迭代,如果Designer 能提前获得更多、更全面的工艺信息,则这个过程可以大大简化和加速,进而提升良率、降低成本。

(图片来自麦肯锡官网)

东方晶源基于坚实的计算光刻平台PanGen和丰富产业实践经验,创新性的开发了PanGen DMC(Design Manufacturability Check)产品,其内嵌D2C(Design To Contour)快速光刻反馈引擎,能够将FAB 全套OPC Recipe解决方案以AI模型的方式进行打包,从而使用户可以基于原始Design快速、精准估计该Design 最终硅片上的形貌(Contour),进而提前预知设计版图存在的潜在风险。

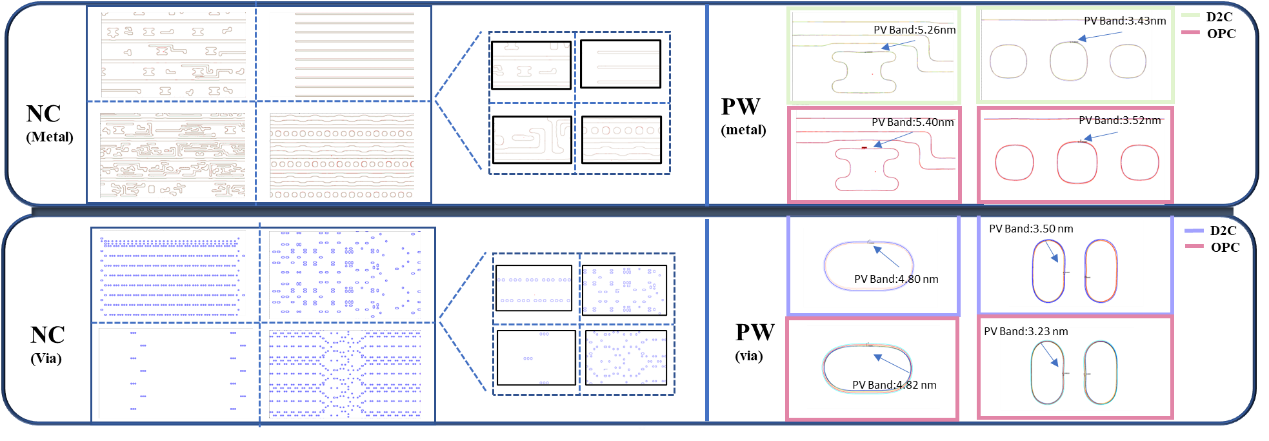

D2C引擎能够准确的捕捉整套OPC Recipe的行为,给出和完整OPC Recipe非常接近的Contour结果。从下图可以直观的看出,对不同几何特性的Metal和Via工艺层(Layer), D2C给出的Contour和完整OPC Recipe给出的Contour几乎是贴合在一起,即便是综合计算多个工艺条件下的PV Band(Peak and Valey Band),其结果也是非常接近。

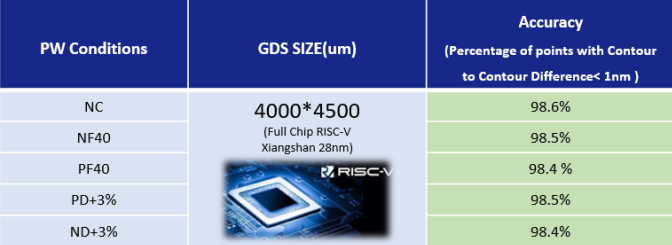

以一个完整的28nm节点的RISC-V full chip版图为例,D2C给出的Contour和完整OPC Recipe给出的Contour在不同的工艺条件下(PW conditions)的差距基本上小于1nm,并且运算速度远高于完整OPC Recipe,目前版本实测可提速约 80倍。

随着工艺技术日趋复杂,仅仅靠抽象的规则很难将整套工艺的方方面面全都包括进去,因此一个设计版图通过了基于规则的DRC(Design Rule Check)检查并不意味着其可以在工艺端有良好的表现。而PanGen DMC可以预估设计版图最终的光刻形貌,以更加全面、直观的方式提供工艺端的反馈。此外,DRC检查只是告知一个非黑即白的是否违例的结论,一定程度的违例到底会在工艺端带来多大的影响无从得知。而PanGen DMC基于模型能以非常可视化的方式将影响呈现给用户,帮助用户在实践中根据情况对违例处理进行权衡。故而无论对制造端还是设计端,该产品都可以作为现有DRC(Design Rule Check)工具非常有力的补充,在尊重客户已有工作流程的基础上,帮助客户于DRC检查之外更全面的发现版图在工艺可制造性方面的风险,从而加速迭代、降低时间成本,使新的芯片产品在流片过程中能更快拉升良率,更早推向市场。

PanGen dFO——有效消除坏点,提供更彻底的OPC解决方案

晶圆厂在进行OPC时,会针对具体技术节点各工艺层版图的特性,开发OPC Recipe,例如针对28nm技术节点金属层的OPC Recipe。OPC Recipe本质上是一系列优化策略和参数的设置,能够将输入的整个工艺层的原始版图转化为可以在硅片上按设想形貌成像的掩模版图形。OPC Recipe在开发时会考虑该技术节点下多样化的图形输入,并对设计版图实施OPC优化之后进行光刻仿真检测(LRC),如果检测发现有坏点,则对OPC Recipe进行迭代改进,从而尽可能的使OPC Recipe可以完全应对各种设计版图。当OPC Recipe确定后,就会从晶圆厂的研发部门转移到量产部门,投入到大规模生产中。

但是金无足赤,器无完器,实践中OPC Recipe可能并不能很好的覆盖一些版图的某些位置的图案,其输出的掩模版图形无法给出预期成像结果,从而产生坏点(Hot Spot),影响最终芯片良率,这是晶圆厂需要面对的实际痛点问题。此时就需要根据光刻仿真检测(LRC)的反馈,对该处掩模版图形做局部的修改,即Mask Repair。

Mask Repair能有效的帮助OPC 工程师消除坏点,但是有可能对mask局部修改过大,导致该处图形形状极端,从而对掩模版制造的工艺扰动过于敏感,产生新的问题;并且有些情况下,设计版图的形貌天然就会导致该处成像质量较差,此时反复迭代Repair Mask 就很难收敛到一个比较理想的结果 !

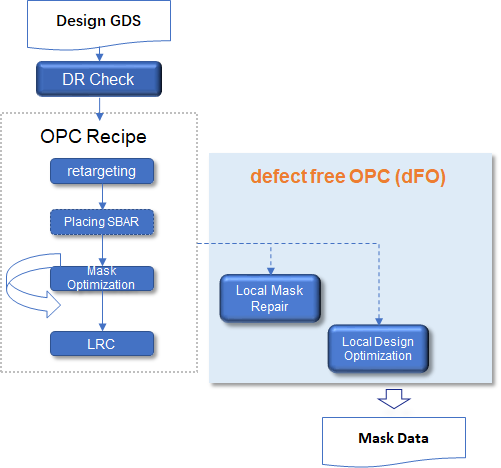

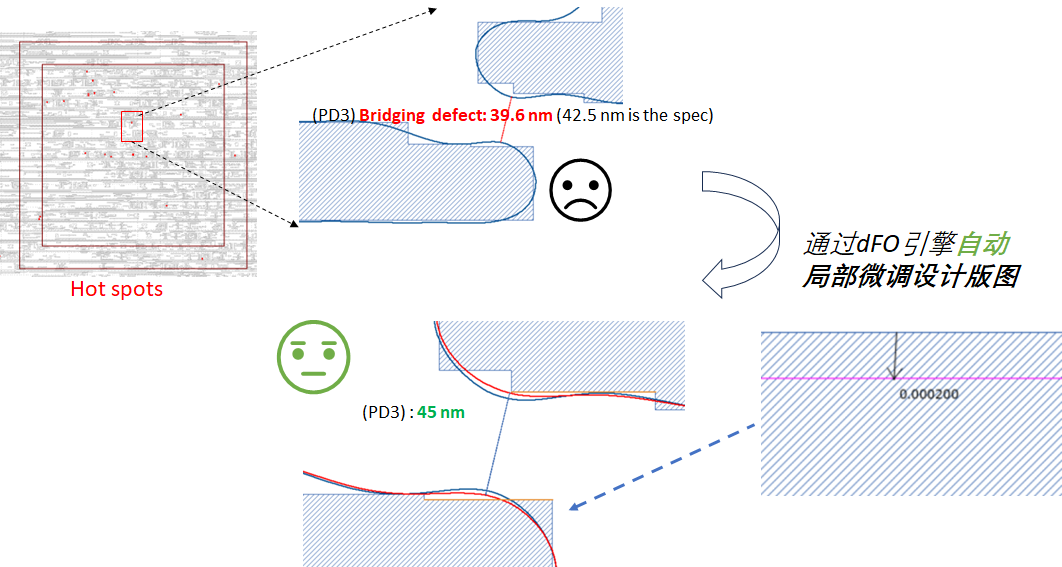

东方晶源在现有的计算光刻平台PanGen 基础之上,创新性的把局部Mask Repair 拓展到局部的Design微调,推出PanGen dFO (defect free OPC)产品,以一种递进式的策略,持续自动查缺补漏,可提供更彻底的OPC 解决方案。 实践中针对全芯片光刻仿真检测(LRC)发现的坏点,首先采用局部Mask Repair 的办法,如果能直接解决,则针对该坏点的处理结束。如果不能解决,则通过局部自动微调设计的方式来解决该坏点。例如开始有1000 个坏点,可能有相当一部分已经在第一步局部Mask Repair 的过程中被解决, 只有剩下少部分坏点会进入下一步局部微调设计的步骤中。

根据光刻仿真反馈局部自动微调设计版图,对整个设计的改动微乎其微,对芯片设计本身的功能不会有影响,但是对实际的光刻却能产生非常正面的帮助,属于四两拨千斤,针对某些顽固坏点可以起到拨云见日的效果。如下图所示,0.2 nm 的Design 自动微调,成效显著:

下面测试实例基于 28nm 节点一个 4000um * 4500 um 完整RISC-V芯片M2层,可以看出通过PanGen dFO的持续改进,坏点数量有了非常显著的减少。

OPC在半导体产业链中发挥着极其关键的战略枢纽作用,如果没有OPC所有先进节点的晶圆厂将失去将芯片设计转化为芯片产品的能力,但难解的坏点就像晴天上的几朵乌云,制约着OPC Recipe更普适的发挥作用,从而影响晶圆厂的生产效率和良率。PanGen dFO 基于东方晶源已有的技术要素,创新性的将局部Mask Repair和局部的Design微调递进式的整合在一起,持续查缺补漏,化解OPC Recipe 难解的顽固坏点,拨云见日,为晶圆厂更高效的提升良率提供更多助力!

芯耀

芯耀

826

826

下载ECAD模型

下载ECAD模型