Chiplet封装的产品介绍

以下介绍几款国内外使用Chiplet封装技术的代表产品,包括CPU、GPU和ASIC芯片。

1. 苹果M1-Ultra CPU:

2022年3月9日,苹果推出自研的M1-Ultra处理器芯片,通过UltraFusion架构将两个M1 Max芯片拼在一起,使芯片的各项硬件指标翻倍,性能也得到大幅提升。

2. AMD RX 7000系列GPU:

2022年11月4日,AMD发布新一代旗舰GPU RX 7000系列,采用新一代RDNA 3架构,首批发布的两款型号为RX 7900 XTX和RX 7900 XT。RDNA 3架构采用Chiplet设计,相比于上一代每瓦性能可以提升50%;内置AI加速单元,性能提升了2.7倍。

3. 寒武纪思远370系列ASIC:

2021年11月3日,寒武纪发布第三代云端AI芯片思元370,基于7nm工艺打造,是寒武纪首款采用chiplet技术的AI芯片;思元370集成了390亿个晶体管,最大算力256TOPS,是寒武纪第二代产品思元270算力的2倍。

4. 壁仞科技BR100系列GPU:

2022年8月9日,壁仞科技发布首款通用GPU芯片BR100,采用7nm工艺,集成770亿晶体管,使用Chiplet与CoWoS 2.5D封装技术。BR100算力达到1000T以上、8位定点算力达到2000T以上,单芯片峰值算力达到960PFLOPS,FP32算力超越英伟达在售旗舰GPU。

Chiplet封装技术面临的挑战

1. 芯片设计和验证工具的更新:

Chiplet对上游的设计和验证提出了新的要求,由于Chiplet芯粒间的堆叠和互联,在进行设计时不仅要考虑不同的制程工艺、不同架构的芯粒进行集成,还要加入高速互联总线和各类接口等;相比于传统直接设计复杂的大芯片,Chiplet技术对于EDA软件的要求明显不同;目前全球前三大EDA软件厂商已经在布局对应的平台。

2. 先进封装技术升级:

传统封装一般通过线路焊接的方式进行,Chiplet为保证芯粒之间更快的互联速度,会采用2.5D/3D等无需线路焊接的先进封装方式;从2D、2.5D到3D,可以形象理解为平面上建高楼,楼建的越高,住的人也越多,能装下的晶体管也更多;目前先进封装技术发展较为成熟,已经具备了实现Chiplet的条件。

3. 互联协议标准统一:

各大芯片公司在芯粒接口的互联协议上各自为战,每家公司选择不同的技术线路和标准,往往是基于公司过往的技术积累,并不能通用;碎片化定制化的接口标准对于Chiplet行业发展极为不利;为了解决这一难题,2022年3月2日,英特尔、AMD、台积电、微软、ARM等十大行业巨头宣布成立UCIe联盟;UCIe联盟的成立为Chiplet技术的发展奠定了最关键的基础条件。

支持Chiplet的底层封装技术

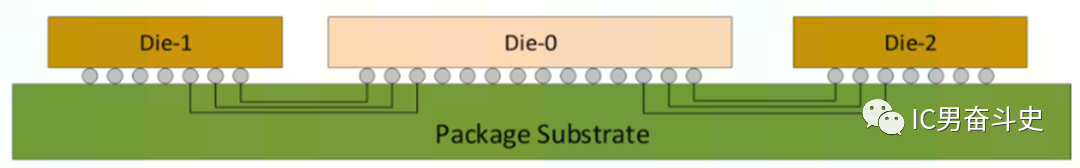

1MCM (Multi-Chip Module)

MCM一般是指通过Substrate (封装基板) 走线将多个芯片互联的技术。通常来说走线的距离和范围可以在10mm~25mm,线距线宽大约10mm量级,单条走线带宽大约10Gbit/s量级。由于MCM可以通过基板直接连接各个芯片,通常封装的成本会相对较低。但是由于走线的线距线宽比较大,封装密度相对较低,接口速率相对较低,延时相对较大。

MCM封装结构示意图

2CoWoS (Chip-on-Wafer-on-Substrate)

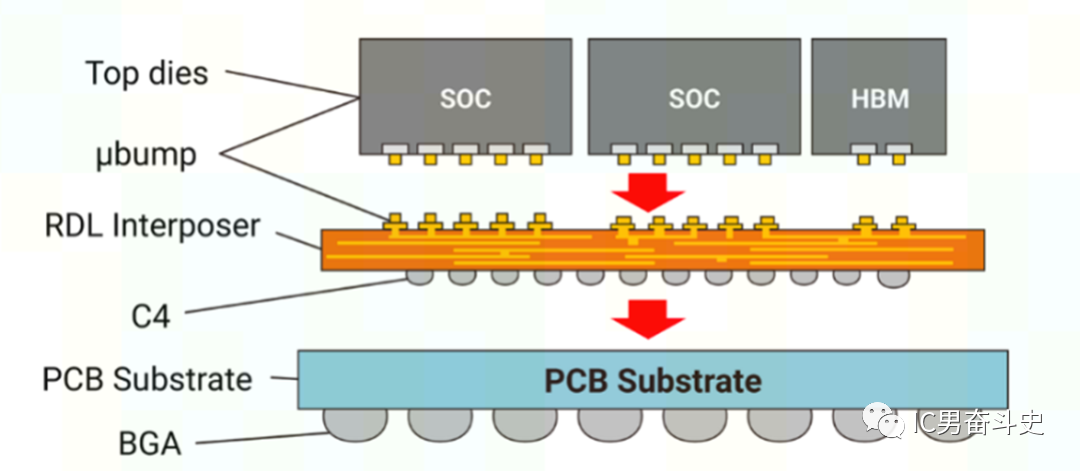

CoWoS是TSMC主导的,基于interposer (中间介质层) 实现的2.5D封装技术。其中interposer采用成熟制程的芯片制造工艺,可以提供相比MCM更高密度和更大速率的接口。目前TSMC主流的CoWoS技术包括CoWoS-S、 CoWoS-R以及CoWoS-L三种。

1. CoWoS-S封装技术

CoWoS-S是基础的CoWoS技术,可以支持超高集成密度,提供不超过两倍掩膜版尺寸的interposer层,通常用于集成HBM (High Bandwidth Memory) 等高速高带宽内存芯片。

CoWoS-S封装结构示意图

2. CoWoS-R封装技术

基于前述CoWoS-S技术,引入InFO技术中的RDL (Redistribution Layer),RDL中介层由聚合物和铜迹线组成,具有相对机械柔韧性,而这种灵活性增强了封装连接的可靠性,并允许新封装可以扩大其尺寸以满足更复杂的功能需求,从而有效支持多个Chiplet之间进行高速可靠互联。

CoWoS-R封装结构示意图

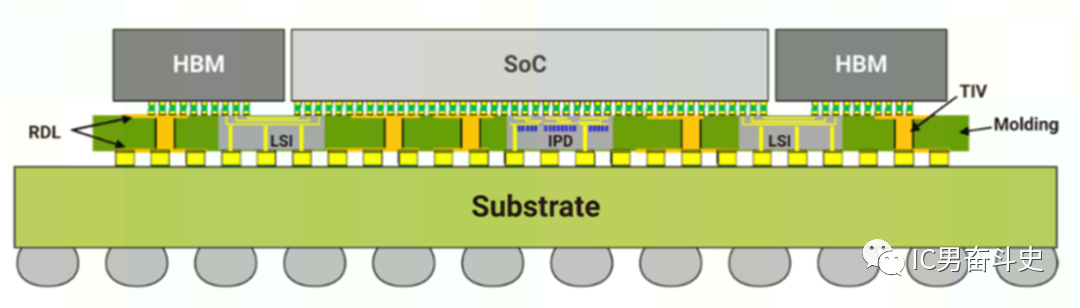

3. CoWoS-L封装技术

在上述CoWoS-S和InFO技术的基础上,引入LSI (Local Silicon Interconnect) 技术,LSI芯片在每个产品中可以具有多种连接架构 (例如SoC到SoC、SoC到小芯片、SoC到HBM 等),也可以重复用于多个产品,提供更灵活和可复用的多芯片互联架构。

CoWoS-L封装结构示意图

相比于MCM,CoWoS技术可以提供更高的互联带宽和更低的互联延时,从而获得更高的性能;同时受限于interposer的尺寸 (通常为2倍掩膜版最大尺寸),可以提供的封装密度上限相对比较有限,并且由于interposer的引入,需要付出额外的制造成本和更高的技术复杂度,以及随之而来的整体良率的降低。

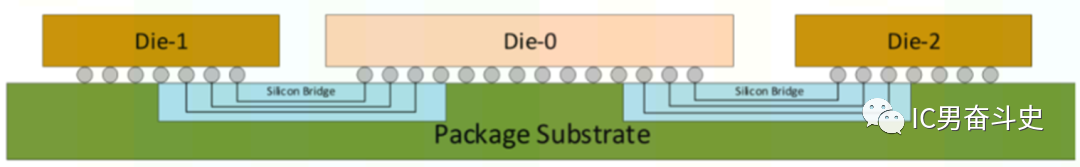

EMIB (Embedded Multi-die Interconnect Bridge)

EMIB是Intel主导的2.5D封装技术,使用多个嵌入式桥接芯片(Silicon Bridge) 实现芯粒间的高速互联;这些桥接芯片包含多个路由层,同时内嵌至封装基板,达到高效和高密度的封装。由于不再使用interposer作为中间介质,可以去掉原有连接至interposer所需要的TSVs,以及由于interposer尺寸所带来的封装尺寸的限制,可以获得更好的灵活性和更高的集成度。

总体而言,相比于前述介绍的MCM、CoWoS、InFO/LSI等技术,EMIB技术要更为优雅和经济高效,而且能够获得更高的集成度和制造良率。但是EMIB需要封装工艺配合桥接芯片,技术门槛和复杂度都比较高。

图EMIB封装结构示意图

芯耀

芯耀

1517

1517

-1-%E5%89%AF%E6%9C%AC.jpg?x-oss-process=image/resize,m_fill,w_128,h_96)